Philips Semiconductors

SC16C754

Quad UART with 64-byte FIFO

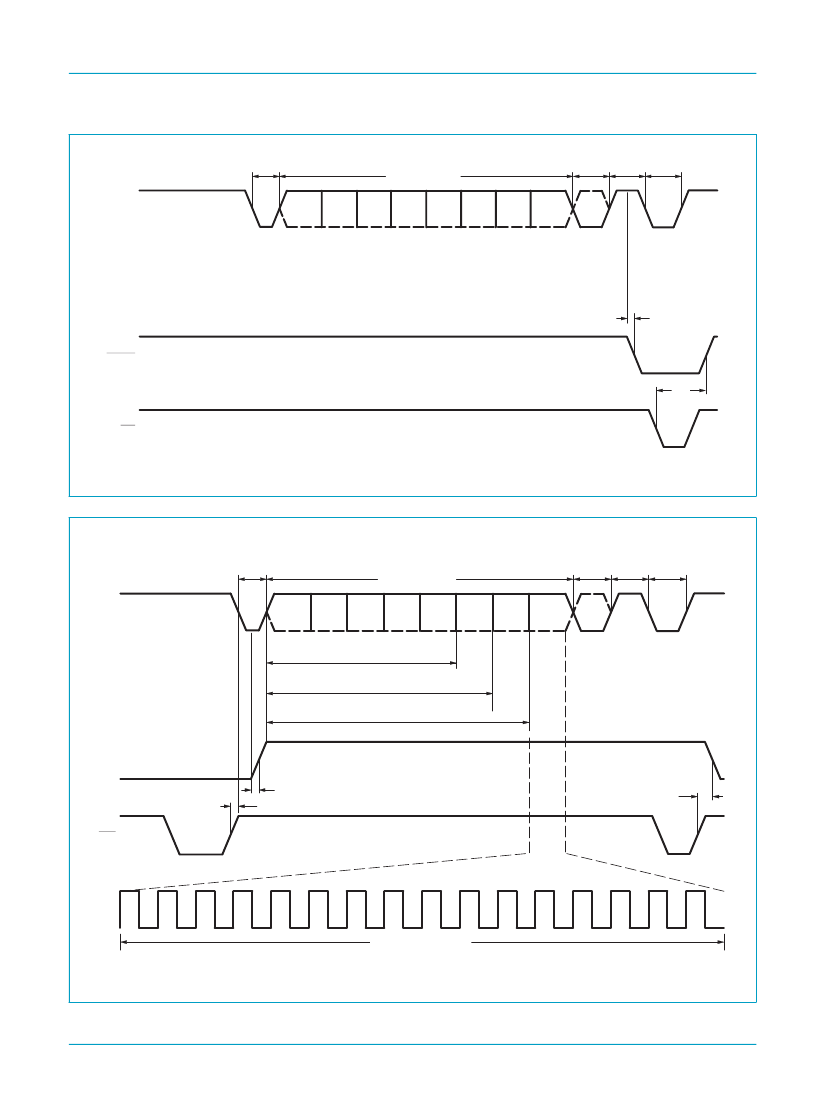

START

BIT

DATA BITS (5鈥?)

PARITY

BIT

STOP

BIT

RX

D0

D1

D2

D3

D4

D5

D6

D7

FIRST BYTE THAT

REACHES THE

TRIGGER LEVEL

t

25d

ACTIVE

DATA

READY

t

26d

RXRDY

IOR

ACTIVE

002aaa115

Fig 20. Receive ready timing in FIFO mode.

START

BIT

DATA BITS (5鈥?)

PARITY

BIT

STOP

BIT

NEXT

DATA

START

BIT

TX

D0

D1

D2

D3

D4

D5

D6

D7

5 DATA BITS

6 DATA BITS

7 DATA BITS

INT

ACTIVE TX READY

t

22d

t

23d

IOW

ACTIVE

t

24d

ACTIVE

16 BAUD RATE CLOCK

002aaa116

Fig 21. Transmit timing.

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

40 of 49