DS26502 T1/E1/J1/64KCC BITS Element

8. T1 FRAMER/FORMATTER CONTROL REGISTERS

The T1 framer portion of the DS26502 is configured via a set of five control registers. Typically, the

control registers are only accessed when the system is first powered up. Once the DS26502 has been

initialized, the control registers will only need to be accessed when there is a change in the system

configuration. There are two receive control registers (T1RCR1 and T1RCR2), two transmit control

registers (T1TCR1 and T1TCR2), and a common control register (T1CCR). Each of these registers is

described in this section.

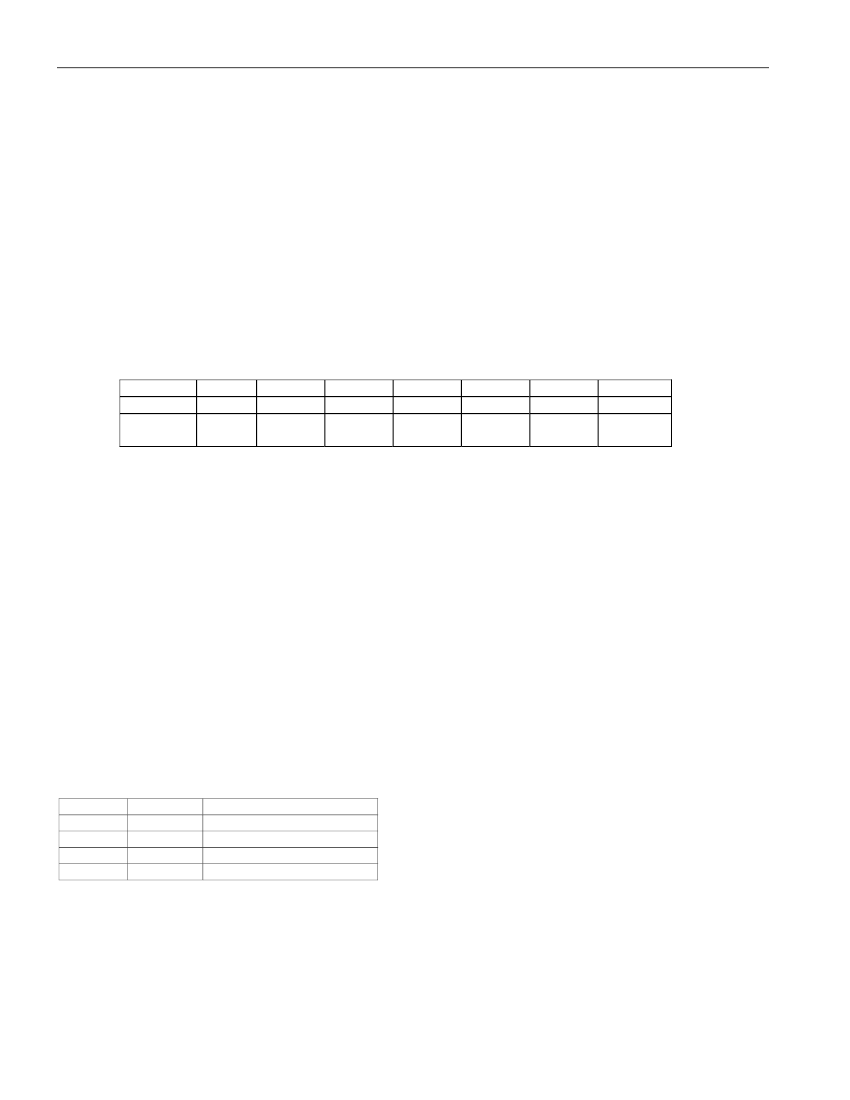

8.1 T1 Control Registers

Register Name:

Register Description:

Register Address:

Bit #

Name

Default

HW

Mode

7

鈥?/div>

0

0

T1RCR1

T1 Receive Control Register 1

03h

6

ARC

0

0

5

OOF1

0

0

4

OOF2

0

0

3

SYNCC

0

0

2

SYNCT

0

0

1

SYNCE

0

0

0

RESYNC

0

0

Bit 0: Resynchronize (RESYNC).

When toggled from low to high, a resynchronization of the receive side framer is initiated.

Must be cleared and set again for a subsequent resync.

Bit 1: Sync Enable (SYNCE)

0 = auto resync enabled

1 = auto resync disabled

Bit 2: Sync Time (SYNCT)

0 = qualify 10 bits

1 = qualify 24 bits

Bit 3: Sync Criteria (SYNCC)

In D4 Framing Mode:

0 = search for Ft pattern, then search for Fs pattern

1 = cross couple Ft and Fs pattern

In ESF Framing Mode:

0 = search for FPS pattern only

1 = search for FPS and verify with CRC6

Bits 4 and 5: Out Of Frame Select Bits (OOF2, OOF1)

OOF2

0

0

1

1

OOF1

0

1

0

1

Out Of Frame Criteria

2/4 frame bits in error

2/5 frame bits in error

2/6 frame bits in error

2/6 frame bits in error

Bit 6: Auto Resync Criteria (ARC)

0 = resync on OOF or RLOS event

1 = resync on OOF only

Bit 7: Unused, must be set = 0 for proper operation.

39 of 124