DS26502 T1/E1/J1/64KCC BITS Element

12. E1 SYNCHRONIZATION STATUS MESSAGE

The DS26502 provides access to both the transmit and receive Sa/Si bits. In E1, the Sa bits are used to

transmit and receive the SSM. The primary method to access the Sa (and Si) bits is based on CRC4

multiframe access. An alternate method is based on double-frame access.

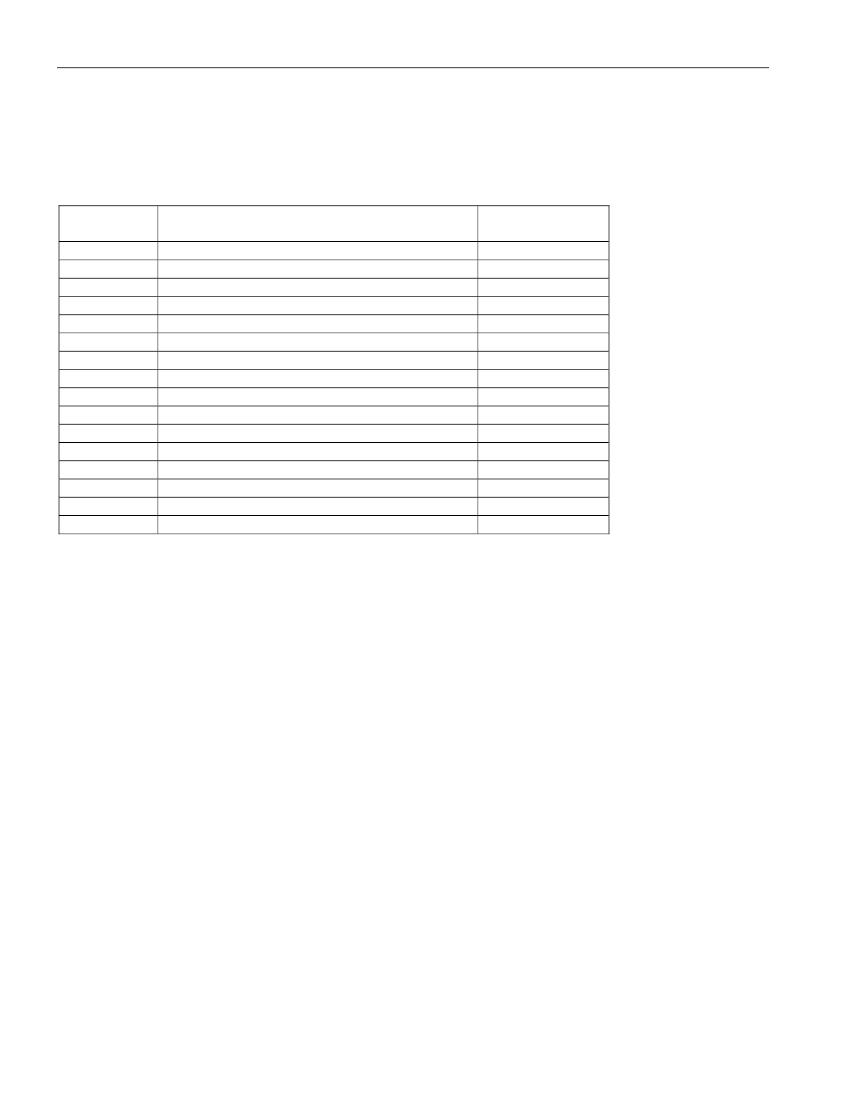

Table 12-1. E1 SSM Messages

QUALITY

LEVEL

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

DESCRIPTION

Quality unknown (existing sync network)

Reserved

Rec. G.811 (Traceable to PRS)

Reserved

SSU-A (Traceable to SSU type A, see G.812)

Reserved

Reserved

Reserved

SSU-B (Traceable to SSU type B, see G.812)

Reserved

Reserved

Synchronous Equipment Timing Source

Reserved

Reserved

Reserved

Do not use for synchronization

Sa BIT

MESSAGE

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

01111

In E1 operation, SSMs are transmitted using one of the Sa bits鈥擲a4, Sa5, Sa6, Sa7, or Sa8. The SSM is

transmitted MSB first in the first frame of the multiframe. Each multiframe will contain two SSMs, one in

each sub-multiframe. An SSM is declared valid when the message in three sub-multiframes are alike.

12.1 Sa/Si Bit Access Based on CRC4 Multiframe

On the receive side, there is a set of eight registers (RSiAF, RSiNAF, RRA, RSa4 to RSa8) that report the

Si and Sa bits as they are received. These registers are updated on CRC4 multiframes. A bit in status

register 4 (SR4.1) indicates the multiframe boundary. The host can use the SR4.1 bit to know when to

read these registers. The user has 2ms to retrieve the data before it is lost. The MSB of each register is the

first received. See the following register descriptions for more details.

On the transmit side, there is also a set of eight registers (TSiAF, TSiNAF, TRA, TSa4 to TSa8) that, via

the transmit Sa bit control register (TSaCR), can be programmed to insert both Si and Sa data. Data is

sampled from these registers with the setting of the transmit multiframe bit in status register 2 (SR4.4).

The host can use the SR4.4 bit to know when to update these registers. It has 2ms to update the data or

else the old data will be retransmitted. The MSB of each register is the first bit transmitted. See the

following register descriptions for details.

63 of 124