DS26502 T1/E1/J1/64KCC BITS Element

4. PIN FUNCTION DESCRIPTION

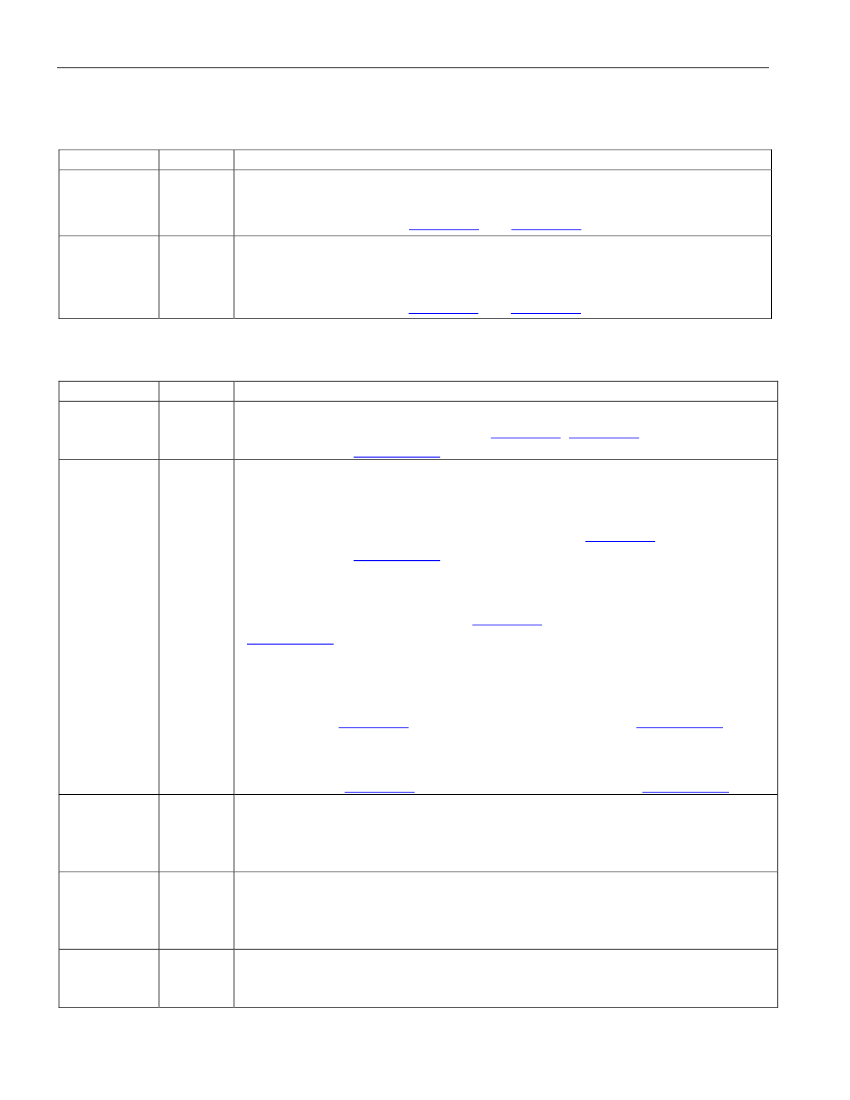

4.1 Transmit PLL

NAME

PLL_OUT

TYPE

O

FUNCTION

Transmit PLL Output.

This pin can be selected to output the 1544kHz,

2048kHz, 64kHz, or 6312kHz output from the internal TX PLL or the internal

signal, TX CLOCK. See

Figure 3-3

and

Figure 3-4.

Transmit Clock Input.

A 64kHz, 1.544MHz, 2.048MHz, or 6312kHz

primary clock. May be selected by the TX PLL mux to either directly drive

the transmit section or be converted to one of the other rates prior to driving

the transmit section. See

Figure 3-3

and

Figure 3-4.

TCLK

I

4.2 Transmit Side

NAME

TSER

TYPE

I

FUNCTION

Transmit Serial Data.

Source of transmit data sampled on the falling edge of

TX CLOCK (an internal signal). See

Figure 3-1, Figure 3-3,

and the transmit

timing diagram (Figure

20-11).

TSYNC, 8kHz Sync, 400Hz Sync

T1/E1 Mode:

In input mode, this pin is sampled on the falling edge of TX

CLOCK (an internal signal) and a pulse at this pin will establish either frame

or multiframe boundaries for the transmit side. See

Figure 3-1

and the transmit

timing diagram (Figure

20-11).

In output mode, this pin is updated on the rising edge of TX CLOCK (an

internal signal) and can be programmed to output a frame or multiframe sync

pulse useful for aligning data. See

Figure 3-1

and the transmit timing diagram

(Figure

20-11).

64KCC Mode:

In input mode, this pin is sampled on the falling edge of TX

CLOCK (an internal signal) and will establish the boundary for the 8kHz

portion of the Composite Clock or the 400Hz boundary based on the setting of

IOCR1.3. See

Figure 3-1

and the transmit timing diagram (Figure

20-11).

In output mode, this pin is updated on the rising edge of TX CLOCK (an

internal signal) and will indicate the 8kHz or 400Hz composite clock

alignment. See

Figure 3-1

and the transmit timing diagram (Figure

20-11).

Transmit Clock Output.

In normal operation this output is the selected

transmit clock from the TX_PLL, TCLK pin or the recovered clock (RCLK).

When remote loopback is enabled this pin will output the recovered network

clock.

Transmit Positive-Data Output.

In T1 or E1 mode, updated on the rising

edge of TCLKO with the bipolar data out of the transmit-side formatter. Can

be programmed to source NRZ data via the output-data format (IOCR1.0)

control bit. In 64KCC or 6312kHz mode this pin will be low.

Transmit Negative-Data Output.

In T1 or E1 mode, updated on the rising

edge of TCLKO with the bipolar data out of the transmit-side formatter. In

64KCC or 6312kHz mode this pin will be low.

14 of 124

TS_8K_4

I/O

TCLKO

O

TPOSO

O

TNEGO

O