N.M.

N.M.

N.M.

N.M.

N.M.

鈥?/div>

0

0

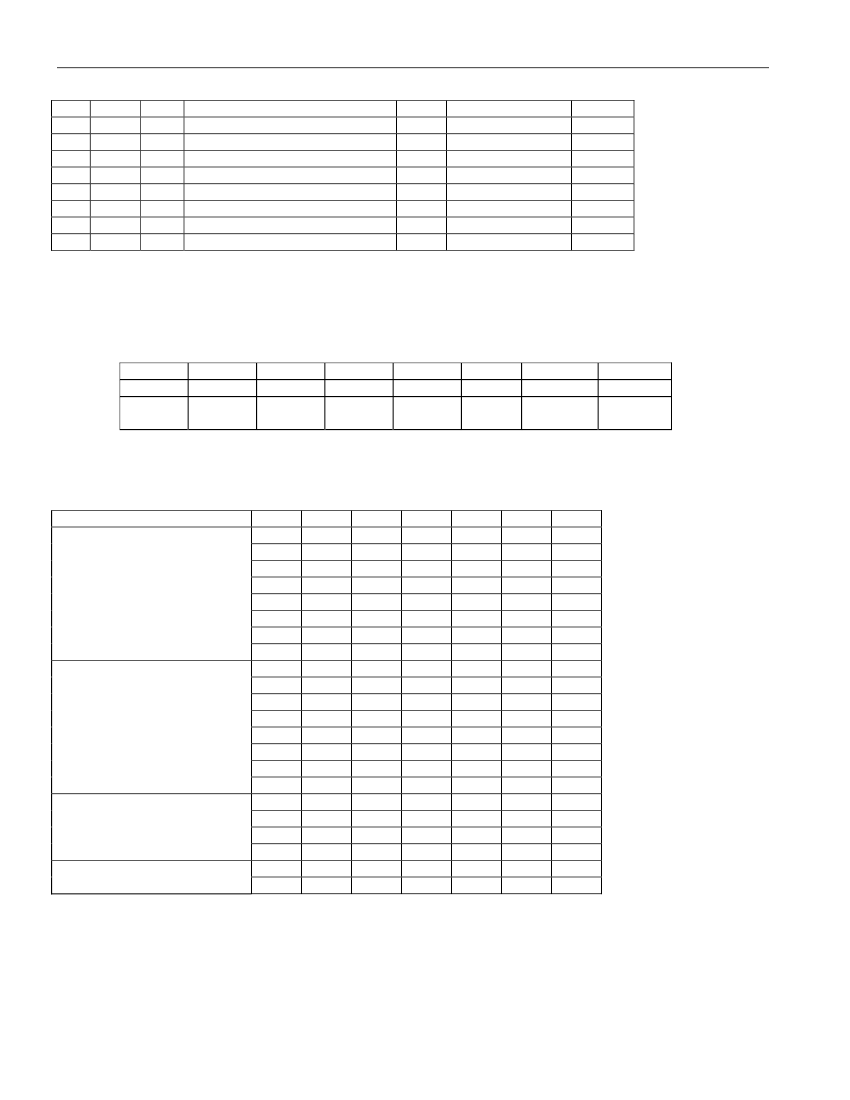

TLBC

Transmit Line Build-Out Control

34h

6

AGCE

0

0

5

GC5

0

0

4

GC4

0

0

3

GC3

0

0

2

GC2

0

0

1

GC1

0

0

0

GC0

0

0

Bits 0 to 5: Gain Control Bits 0鈥? (GC0鈥揋C5).

The GC0 through GC5 bits control the gain setting for the non-automatic

gain mode. Use the tables below for setting the recommended values. The LB (line build-out) column refers to the value in the

L0鈥揕2 bits in LIC1 (Line Interface Control 1) register.

NETWORK MODE

LB

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

4

5

0

1

GC5

1

0

0

1

1

1

0

1

0

0

0

0

1

1

0

1

1

1

1

1

0

0

GC4

0

1

1

0

0

0

1

1

1

1

1

1

0

0

0

1

0

0

0

0

1

1

GC3

0

1

1

0

0

0

0

1

1

0

0

1

0

0

1

1

0

0

1

1

1

1

GC2

1

0

0

0

1

1

0

1

1

1

1

0

0

0

1

1

0

0

0

0

0

0

GC1

1

1

1

0

1

1

1

1

1

0

0

1

1

0

0

1

0

0

1

0

1

1

GC0

0

1

0

0

1

1

1

1

0

1

1

0

0

0

0

1

1

1

0

0

0

0

T1, Impedance Match Off

T1, Impedance Match On

E1, Impedance Match Off

E1, Impedance Match On

Bit 6: Automatic Gain Control Enable (AGCE)

0 = use Transmit AGC, TLBC bits 0鈥? are 鈥渄on鈥檛 care鈥?/div>

1 = do not use Transmit AGC, TLBC bits 0鈥? set nominal level

Bit 7: Unused, must be set = 0 for proper operation.

82 of 124