鈥?/div>

0

0

5

RBOC5

0

0

4

RBOC4

0

0

3

RBOC3

0

0

2

RBOC2

0

0

1

RBOC1

0

0

0

RBOC0

0

0

Bit 0: BOC Bit 0 (RBOC0)

Bit 1: BOC Bit 1 (RBOC1)

Bit 2: BOC Bit 2 (RBOC2)

Bit 3: BOC Bit 3 (RBOC3)

Bit 4: BOC Bit 4 (RBOC4)

Bit 5: BOC Bit 5 (RBOC5)

Bits 6 and 7: This bit position is unused when BOCC.4 = 1.

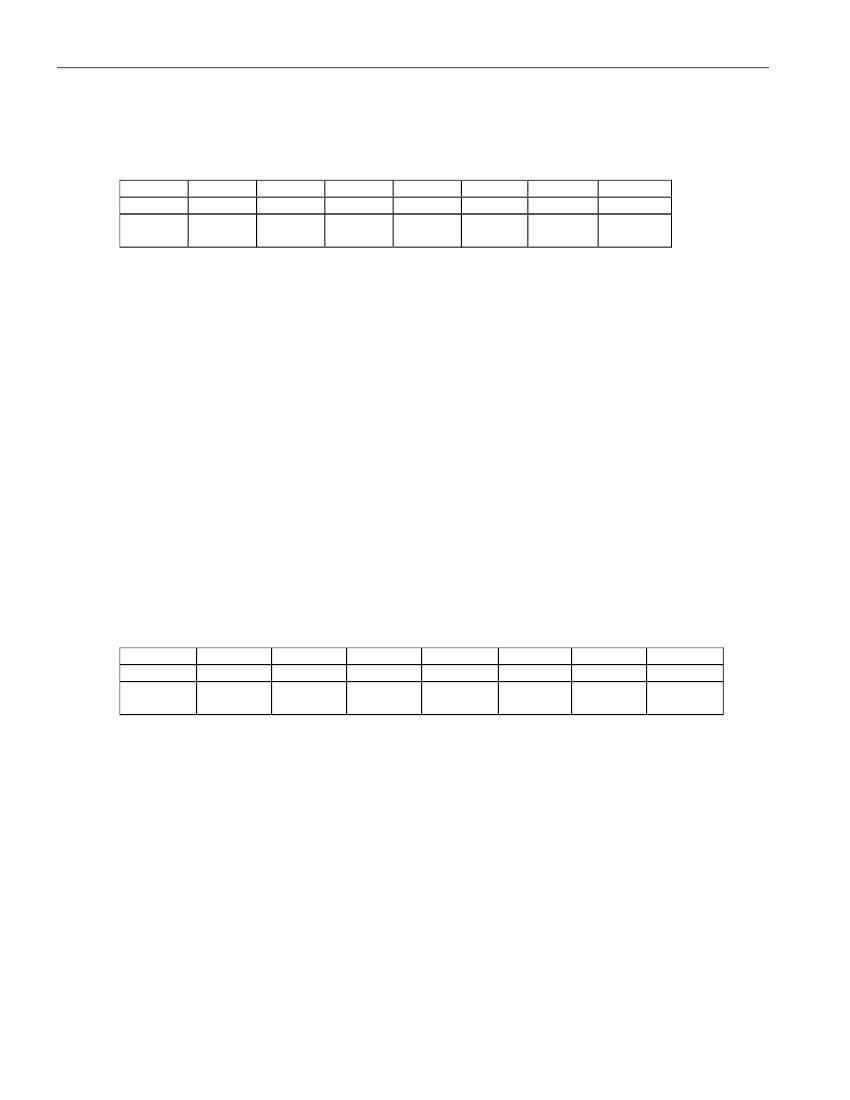

Register Name:

Register Description:

Register Address:

Bit #

Name

Default

HW

Mode

7

RFDLM7

0

0

RFDLM1, RFDLM2

Receive FDL Match Register 1

Receive FDL Match Register 2

52h, 53h

6

RFDLM6

0

0

5

RFDLM5

0

0

4

RFDLM4

0

0

3

RFDLM3

0

0

2

RFDLM2

0

0

1

RFDLM1

0

0

0

RFDLM0

0

0

Bit 0: Receive FDL Match Bit 0 (RFDLM0).

LSB of the FDL Match Code.

Bit 1: Receive FDL Match Bit 1 (RFDLM1)

Bit 2: Receive FDL Match Bit 2 (RFDLM2)

Bit 3: Receive FDL Match Bit 3 (RFDLM3)

Bit 4: Receive FDL Match Bit 4 (RFDLM4)

Bit 5: Receive FDL Match Bit 5 (RFDLM5)

Bit 6: Receive FDL Match Bit 6 (RFDLM6)

Bit 7: Receive FDL Match Bit 7 (RFDLM7).

MSB of the FDL Match Code.

57 of 124