TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

external interface, XINTF (F2812 only) (continued)

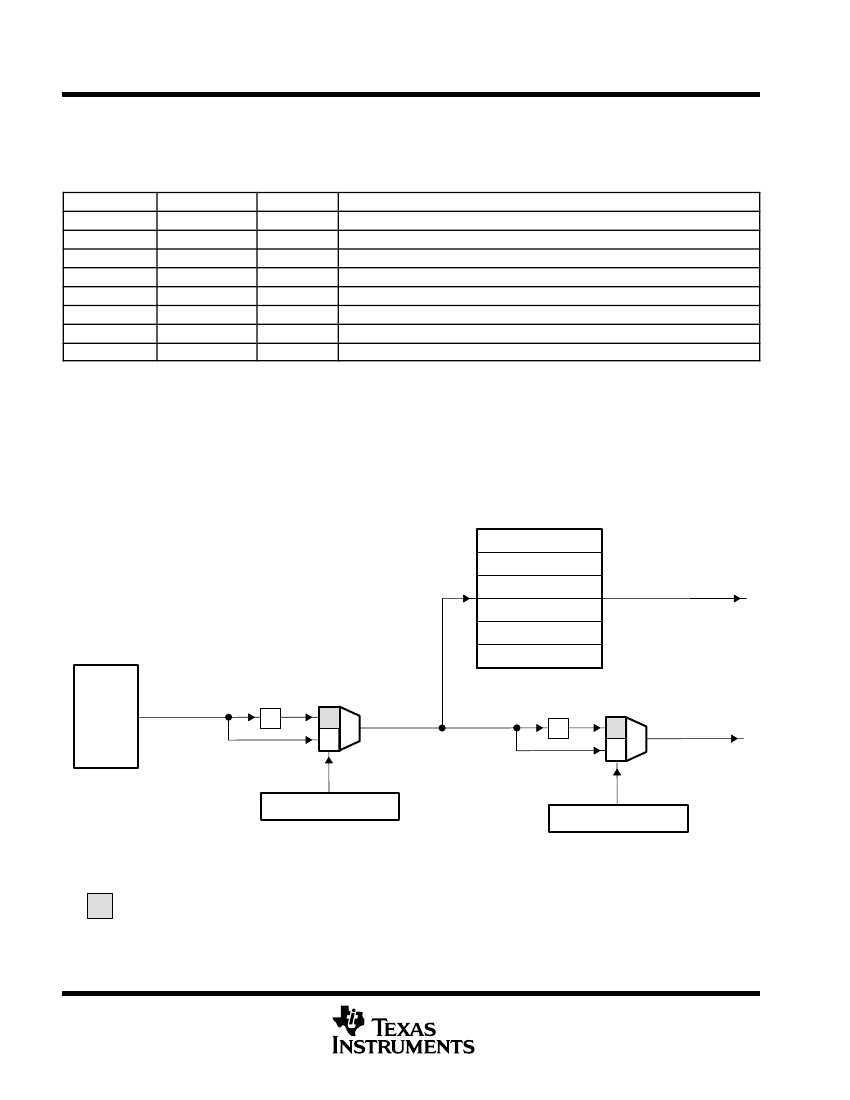

The operation and timing of the external interface, can be controlled by the registers listed in Table 13.

Table 13. XINTF Configuration and Control Register Mappings

NAME

XTIMING0

XTIMING1

XTIMING2

XTIMING6

XTIMING7

XINTCNF2

XBANK

XREVISION

ADDRESS

0x0000鈥?B20

0x0000鈥?B22

0x0000鈥?B24

0x0000鈥?B2C

0x0000鈥?B2E

0x0000鈥?B34

0x0000鈥?B38

0x0000鈥?B3A

SIZE (x16)

2

2

2

2

2

2

1

1

XINTF Timing Register, Zone 0

XINTF Timing Register, Zone 1

XINTF Timing Register, Zone 2

XINTF Timing Register, Zone 6

XINTF Timing Register, Zone 7

XINTF Configuration Register

XINTF Bank Control Register

XINTF Revision Register

DESCRIPTION

timing registers

PRODUCT PREVIEW

XINTF signal timing can be tuned to match specific external device requirements such as setup and hold times

to strobe signals for contention avoidance and maximizing bus efficiency. The timing parameters can be

configured individually for each zone. This allows the programmer to maximize the efficiency of the bus, based

on the type of memory or peripheral that the user needs to access. All XINTF timing values are with respect to

XTIMCLK, which is equal to or one-half of the SYSCLKOUT rate, as shown in Figure 4.

XTIMING0

XTIMING1

XTIMING2

XTIMING6

XTIMING7

XBANK

LEAD/ACTIVE/TRAIL

C28x

CPU

SYSCLKOUT

/2

1

0

0

XTIMCLK

/2

1

XCLKOUT

XINTCNF2 (XTIMCLK)

XINTCNF2 (CLKMODE)

Default Value after reset

Figure 4. Relationship Between XTIMCLK and SYSCLKOUT

28

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443