鈥?On the F2810 and F2812 devices, the VMAP and M0M1MAP modes are set to 鈥?鈥?on reset. The ENPIE mode is forced to 鈥?鈥?on reset.

鈥?Vector map M1 Vector is a reserved mode only.

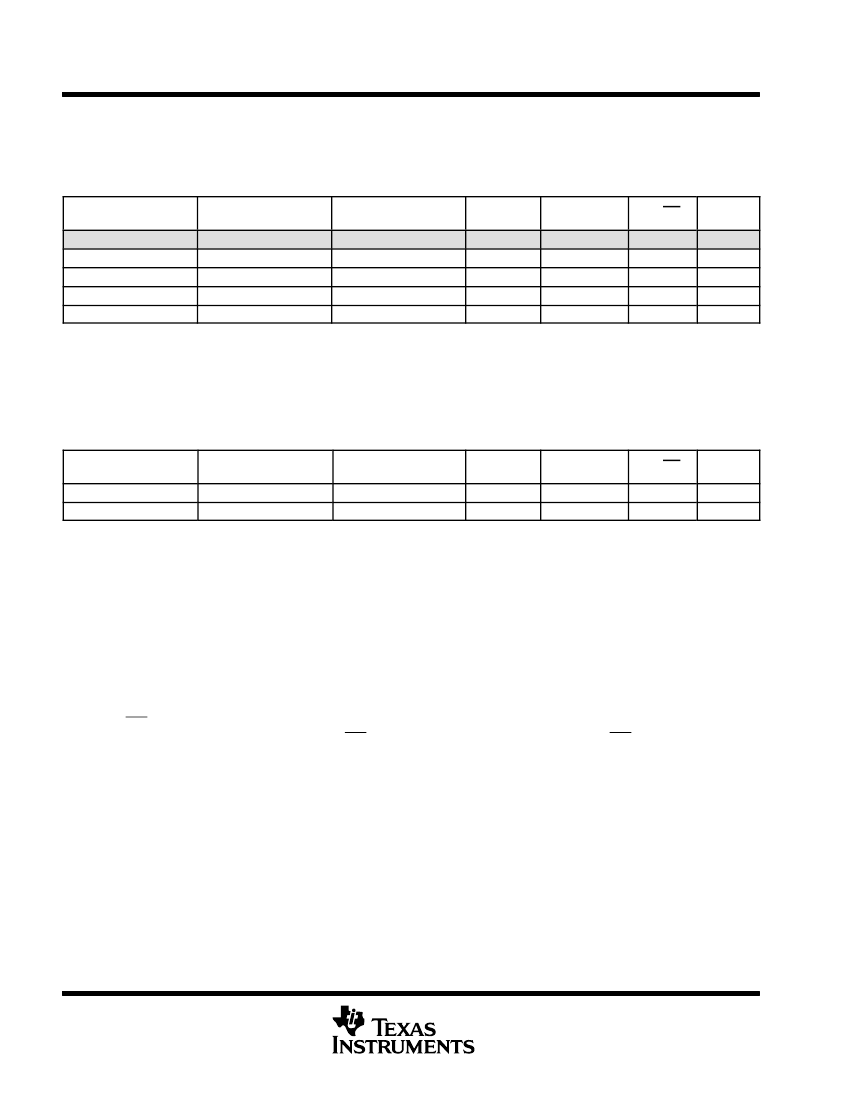

After reset operation, the vector table will be located in the areas listed in Table 20.

Table 20. Vector Table Mapping After Reset Operation

鈥?/div>

VECTOR MAPS

BROM Vector

XINTF Vector搂

RESET FETCHED

FROM

ROM Block

XINTF Zone 7 Block

ADDRESS RANGE

0x3FFFC0鈥?x3FFFFF

0x3FFFC0鈥?x3FFFFF

VMAP

1

1

M0M1MAP

1

1

MP/MC

0

1

ENPIE

0

0

鈥?On the F2810 and F2812 devices, the VMAP and M0M1MAP modes are set to 鈥?鈥?on reset. The ENPIE mode is forced to 鈥?鈥?on reset.

搂 Valid on F2812 only

The vector mapping is controlled by the following mode bits/signals:

VMAP:

This bit is found in Status Register 1 (bit 3). A device reset sets this bit to 1. The state of this

bit can be modified by writing to ST1 or by 鈥淪ETC/CLRC VMAP鈥?instructions.

This bit is found in Status Register 1 (bit 11). A device reset sets this bit to 1. The state of this

bit can be modified by writing to ST1 or by 鈥淪ETC/CLRC M0M1MAP鈥?instructions. This bit

should remain set. M0M1MAP = 0 is reserved for TI testing.

This bit is found in XINTCNF2 Register (bit 8). On the F2812, the default value of this bit, on

reset, is set by the XMP/MC input device signal. On the F2810, XMP/MC is tied low internally.

The state of this bit can be modified by writing to the XINTCNF2 register (address 0x0000

0B34).

This bit is found in PIECTRL Register (bit 0). The default value of this bit, on reset, is set to 鈥?鈥?/div>

(PIE disabled). The state of this bit can be modified by writing to the PIECTRL register

(address 0x0000 0CE0).

M0M1MAP:

MP/MC:

ENPIE:

The external interrupts are configured using the registers listed in Table 27.

36

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443