TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

serial peripheral interface (SPI) module (continued)

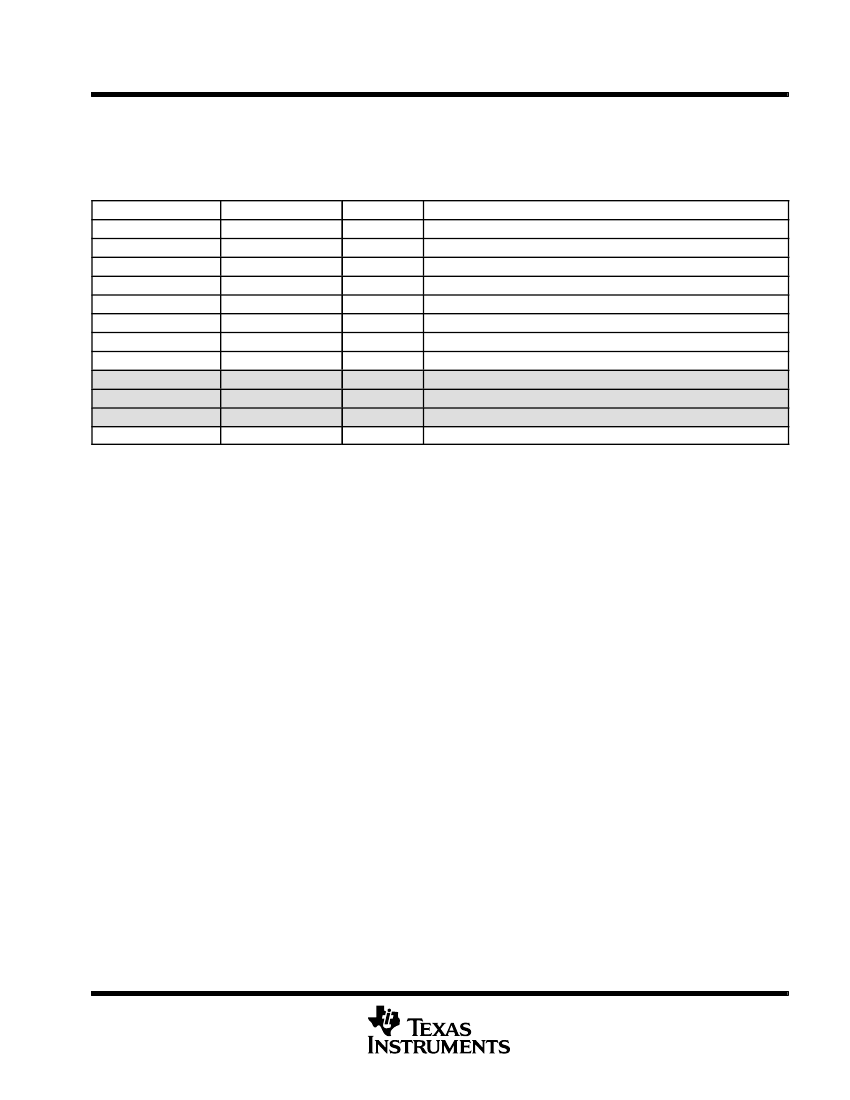

The SPI port operation is configured and controlled by the registers listed in Table 59.

Table 59. SPI Registers

NAME

SPICCR

SPICTL

SPIST

SPIBRR

SPIEMU

SPIRXBUF

SPITXBUF

SPIDAT

SPIFFTX

SPIFFRX

SPIFFCT

SPIPRI

ADDRESS RANGE

0x0000鈥?040

0x0000鈥?041

0x0000鈥?042

0x0000鈥?044

0x0000鈥?046

0x0000鈥?047

0x0000鈥?048

0x0000鈥?049

0x0000鈥?04A

0x0000鈥?04B

0x0000鈥?04C

0x0000鈥?04F

SIZE (x16)

1

1

1

1

1

1

1

1

1

1

1

1

DESCRIPTION

SPI Configuration Control Register

SPI Operation Control Register

SPI Status Register

SPI Baud Rate Register

SPI Emulation Buffer Register

SPI Serial Input Buffer Register

SPI Serial Output Buffer Register

SPI Serial Data Register

SPI FIFO Transmit Register

SPI FIFO Receive Register

SPI Priority Control Register

SPI FIFO Control Register

Note:

The above registers are mapped to Peripheral Frame 2. This space only allows 16-bit accesses. 32-bit

accesses produce undefined results.

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443

83

PRODUCT PREVIEW