TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

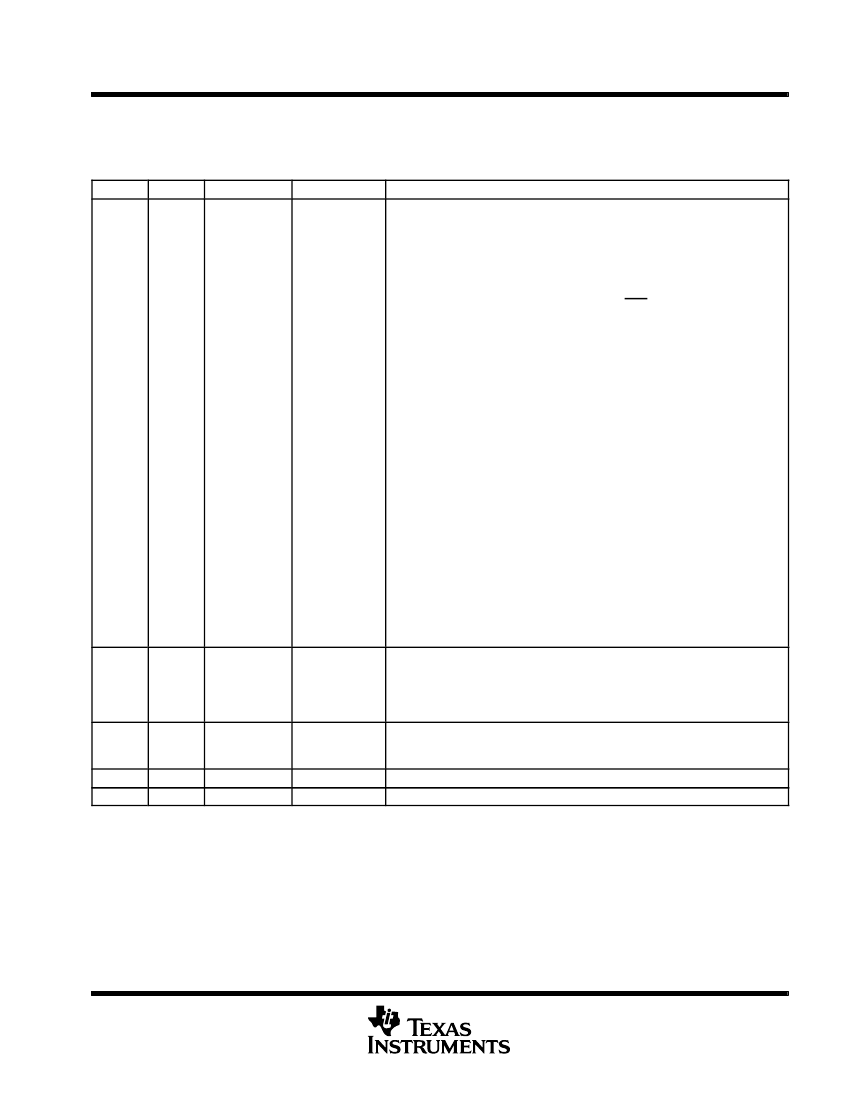

XINTCNF2 register

Table 15. XINTCNF2 Register Bit Definitions

BITS

1,0

TYPE

R/W

NAME

Write

Buffer

Depth

RESET

0,0

DESCRIPTION

The write buffer allows the processor to continue execution without waiting for

XINTF write accesses to complete. The write buffer depth is selectable as follows:

Depth

00

Action

No write buffering. The CPU will be stalled until the write

completes on the XINTF.

Note:

Default mode on reset (XRS).

The XINTF will buffer one word. The CPU is stalled until the

write cycle begins on the XINTF (there could be a read cycle

currently active on the XINTF).

One write will be buffered without stalling the CPU. The CPU

is stalled if a second write follows. The CPU will be stalled

until the first write begins its cycle on the XINTF.

Two writes will be buffered without stalling the CPU. The CPU

is stalled if a third write follows. The CPU will be stalled until

the first write begins its cycle on the XINTF.

01

10

11

The buffered access can be 8, 16, or 32 bits in length. Order of execution is

preserved, e.g., writes are performed in the order they were accepted. The

processor is stalled on XINTF reads until all pending writes are done and the read

access completes. If the buffer is full, any pending reads or writes to the buffer

will stall the processor.

The 鈥淲rite Buffer Depth鈥?can be changed; however, it is recommended that the

write buffer depth be changed only when the buffer is empty (this can be checked

by reading the 鈥淲rite Buffer Level鈥?bits). Writing to these bits when the level is not

zero may have unpredictable results.

2

R/W

CLKMODE

Mode

1

XCLKOUT divide by 2 mode. If this bit is set to 1, XCLKOUT is a divide by 2 of

XTIMCLK. If this bit is set to 0, XCLKOUT is equal to XTIMCLK. All bus timings,

irrespective of which mode is enabled, will start from the rising edge of XCLKOUT.

The default mode of operation on power up and reset is /2 mode.

Turn XCLKOUT off mode. When this bit is set to 1, the XCLKOUT signal is turned

off. This is done for power savings and noise reduction. This bit is set to 0 on a

reset.

Reserved

Reserved

3

R/W

CLKOFF

0

4

5

R

R

Reserved

Reserved

1

0

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443

31

PRODUCT PREVIEW