TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

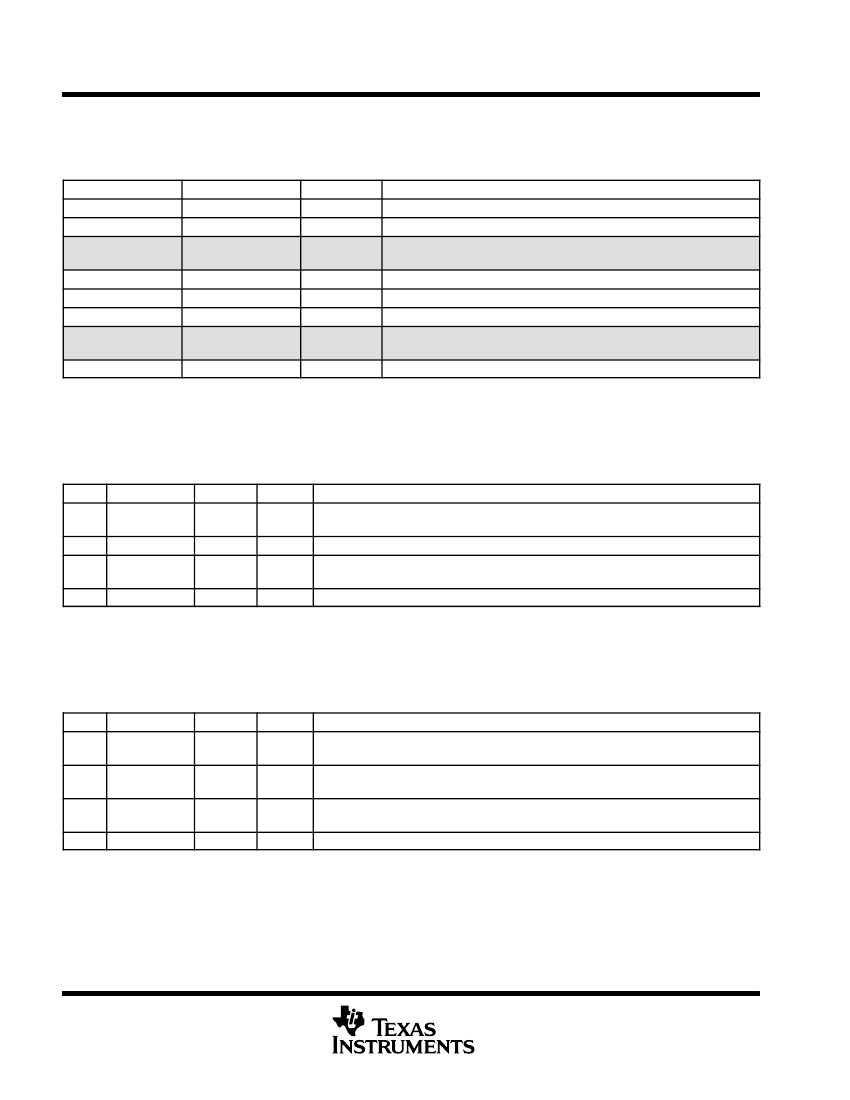

external interrupts

Table 27. External Interrupts Registers

NAME

XINT1CR

XINT2CR

reserved

XNMICR

XINT1CTR

XINT2CTR

reserved

XNMICTR

ADDRESS RANGE

0x0000 7070

0x0000 7071

0x0000 7072

0x0000 7076

0x0000 7077

0x0000 7078

0x0000 7079

0x0000 707A

0x0000 707E

0x0000 707F

SIZE (x16)

1

1

5

1

1

1

5

1

XNMI counter register

XNMI configuration register

XINT1 counter register

XINT2 counter register

XINT1 configuration register

XINT2 configuration register

DESCRIPTION

PRODUCT PREVIEW

Each external interrupt can be enabled/disabled or qualified using positive or negative going edge. The register

bits to control this are described in Table 28.

Table 28. XINT1/2CR Register Bit Definitions

BITS

0

1

2

15:3

NAME

ENABLE

reserved

POLARITY

reserved

TYPE

R/W

R=0

R/W

R=0

RESET

0

0

0

0:0

0

1

Interrupt is selected as negative edge triggered

Interrupt is selected as positive edge triggered

0

1

Interrupt Disabled

Interrupt Enabled

DESCRIPTION

Table 29 shows the bit definitions of the XNMICR register.

Table 29. XNMICR Register Bit Definitions

BITS

0

1

2

15:3

NAME

ENABLE

SELECT

POLARITY

reserved

TYPE

R/W

R/W

R/W

R=0

RESET

0

0

0

0:0

0

1

0

1

0

1

NMI Interrupt Disabled

NMI Interrupt Enabled

Timer 1 Connected To INT13

XNMI Connected To INT13

Interrupt is selected as negative edge triggered

Interrupt is selected as positive edge triggered

DESCRIPTION

42

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443