鈥?/div>

XRS,

WDINT,

Any Enabled Interrupt,

XNMI

XRS,

WDINT,

XINT1,

XNMI,

T1/2/3/4CTRIP,

C1/2/3/4/5/6TRIP,

SCIRXDA,

SCIRXDB,

CANRX,

Debugger搂

XRS,

XNMI,

Debugger搂

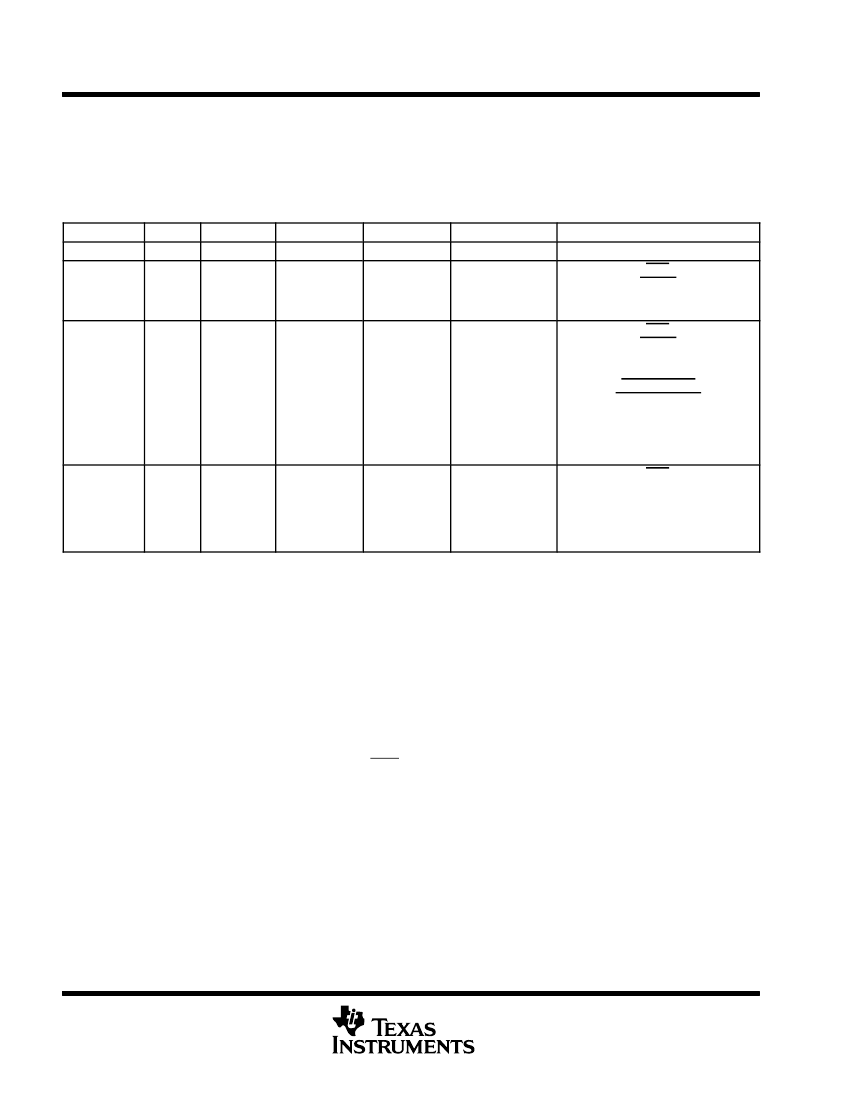

STANDBY

high

0,1

on

(watchdog still

running)

off

off

PRODUCT PREVIEW

HALT

high

1,X

off

(oscillator and

PLL turned

off, watchdog

not functional)

off

off

鈥?The Exit column lists which signals or under what conditions the low power mode will be exited. A low signal, on any of the signals, will exit the

low power condition. This signal must be kept low long enough for an interrupt to be recognized by the device. Otherwise the IDLE mode will

not be exited and the device will go back into the indicated low power mode.

鈥?The IDLE mode on the C28x behaves differently than on the 24x/240x. On the C28x, the clock output from the core (SYSCLKOUT) is still

functional while on the 24x/240x the clock is turned off.

搂 On the C28x, the JTAG port can still function even if the core clock (CLKIN) is turned off.

The various low-power modes operate as follows:

IDLE Mode:

This mode is, exited by any enabled interrupt or an NMI that is recognized

by the processor. The LPM block performs no tasks during this mode as

long as the LPMCR(LPM) bits are set to 0,0.

Only the XRS and XNMI external signals can wake the device from HALT

mode. The XNMI input to the core has an enable/disable bit. Hence, it is

safe to use the XNMI signal for this function.

All other signals (including XNMI) will wake the device from STANDBY

mode if selected by the LPMCR1 register. The user will need to select

which signal(s) will wake the device. The selected signal(s) are also

qualified by the OSCCLK before waking the device. The number of

OSCCLKs is specified in the LPMCR0 register.

HALT Mode:

STANDBY Mode:

54

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443