TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

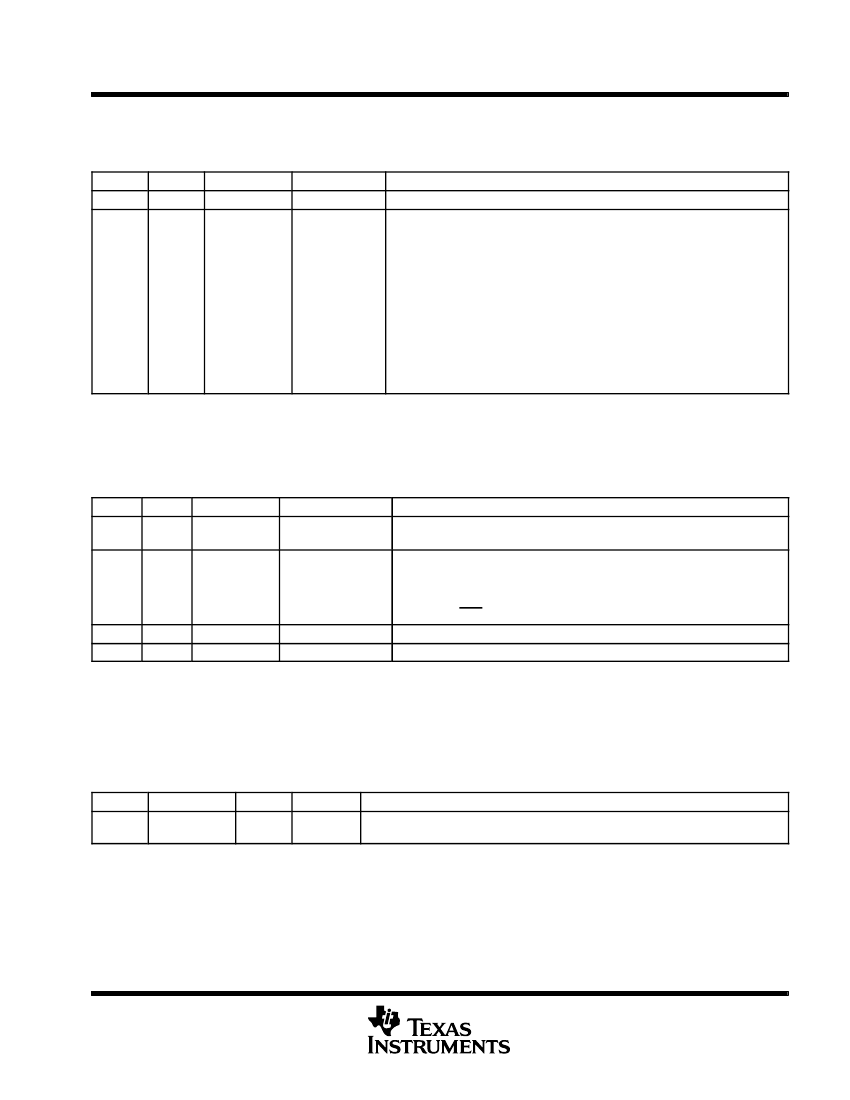

XINTCNF2 register (continued)

Table 15. XINTCNF2 Register Bit Definitions (Continued)

BITS

15:12

18:16

TYPE

X

R/W

NAME

Reserved

XTIMCLK

RESET

0

0,0,1

Reserved

These bits select the fundamental clock for the timing of lead, active and trail

switching operations as defined by the XTIMING and XBANK registers:

Mode

0,0,0

0,0,1

0,1,0

0,1,1

1,0,0

1,0,1

1,1,0

1,1,1

Action

XTIMCLK = SYSCLKOUT/1

XTIMCLK = SYSCLKOUT/2

reserved

reserved

reserved

reserved

reserved

reserved

DESCRIPTION

XBANK register

Table 16. XBANK Register Bit Defintions

BITS

2:0

5:3

TYPE

R/W

R/W

NAME

BANK

BCYC

RESET

1,1,1

1,1,1

DESCRIPTION

These bits specify the XINTF zone for which bank switching is enabled, ZONE

0 to ZONE 7. At reset, XINTF Zone 7 is selected.

These bits specify the number of XTIMCLK cycles to add between any

consecutive access that crosses into or out of the specified zone, be it a read or

write, program or data space. The number of XTIMCLK cycles can be 0 to 14.

On a reset (XRS) the value defaults to 14 cycles.

14:6

15

X

R/W

Reserved

Reserved

1

XREVISION register

The XREVISION register contains a unique number to identify the particular version of XINTF used in the

product. For the F2812, this register will be configured as described in Table 17.

Table 17. XREVISION Register Bit Defintions

BIT(S)

15鈥?

NAME

REVISION

TYPE

R

RESET

0x0004

DESCRIPTION

Current XINTF Revision. For internal use/reference. Test purposes only. Subject to

change.

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443

33

PRODUCT PREVIEW