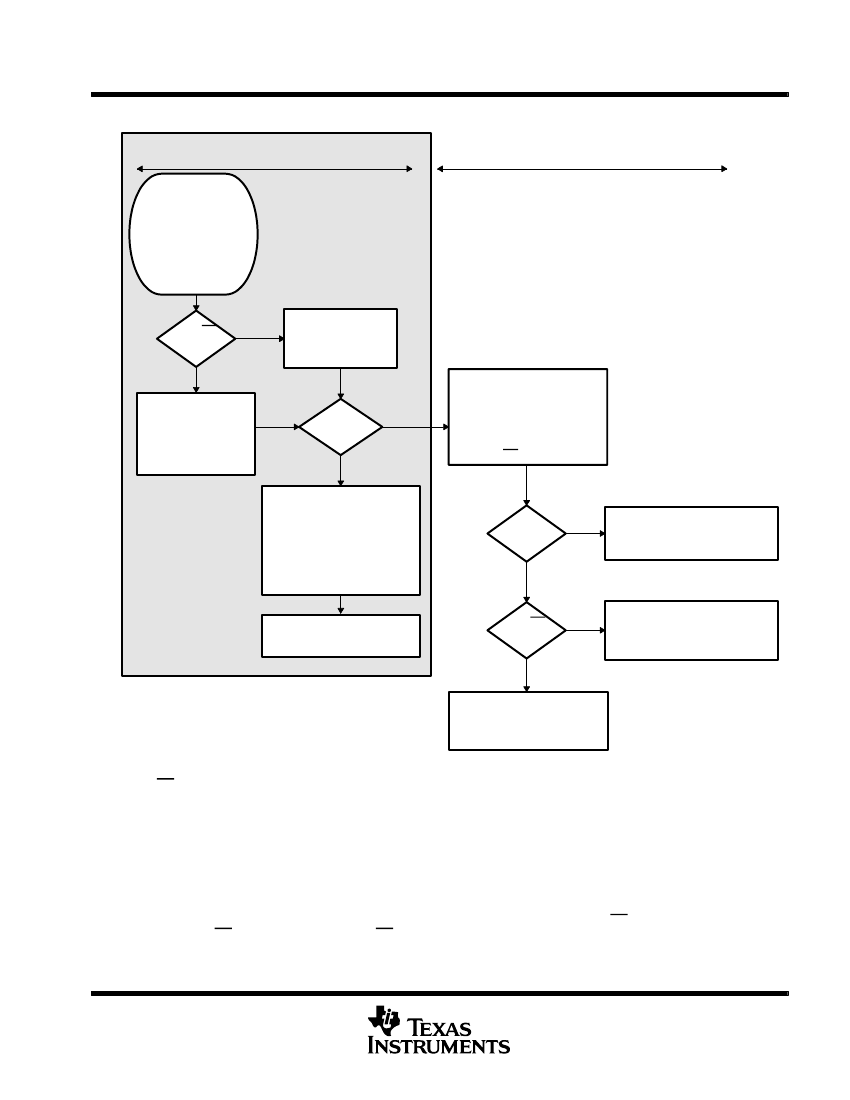

OBJMODE and AMODE State鈥?/div>

VMAP = 1?

PIE Enable (ENPIE = 1)

PIE Vector Table

PIEIERx Registers

CPU IER Register and INTM

No

Vectors (except for reset) will be

fetched from M0 Vector Map搂

Yes

(F2812 Only)

No

Vectors (except for reset) will be

fetched from XINTF Vector Map搂

Vectors (except for reset)

will be

fetched from PIE Vector Map搂

MP/MC

status bit =

0?露

Yes

Vectors (except for reset)

will be Fetched From

BROM Vector Map搂

鈥?The XMP/MC input signal is tied low internally on the F2810.

鈥?The compatibility operating mode of the F2810 and F2812 is determined by a combination of the OBJMODE and AMODE bits in Status

Register 1 (ST1):

Operating Mode

C28x Mode

C2xLP Source-Compatible

C27x Object-Compatible

OBJMODE

1

1

0

AMODE

0

1

0 (Default at reset)

搂 The reset vector is always fetched from either the BROM or XINTF vector map depending on the XMP/MC input signal.

露 The state of the XMP/MC signal is latched into the MP/MC bit at reset, it can then be modified by software.

Figure 7. Reset Flow Diagram

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443

37

PRODUCT PREVIEW

Using

Peripheral

Interrupts?

No