TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B 鈥?APRIL 2001 鈥?REVISED SEPTEMBER 2001

interrupts

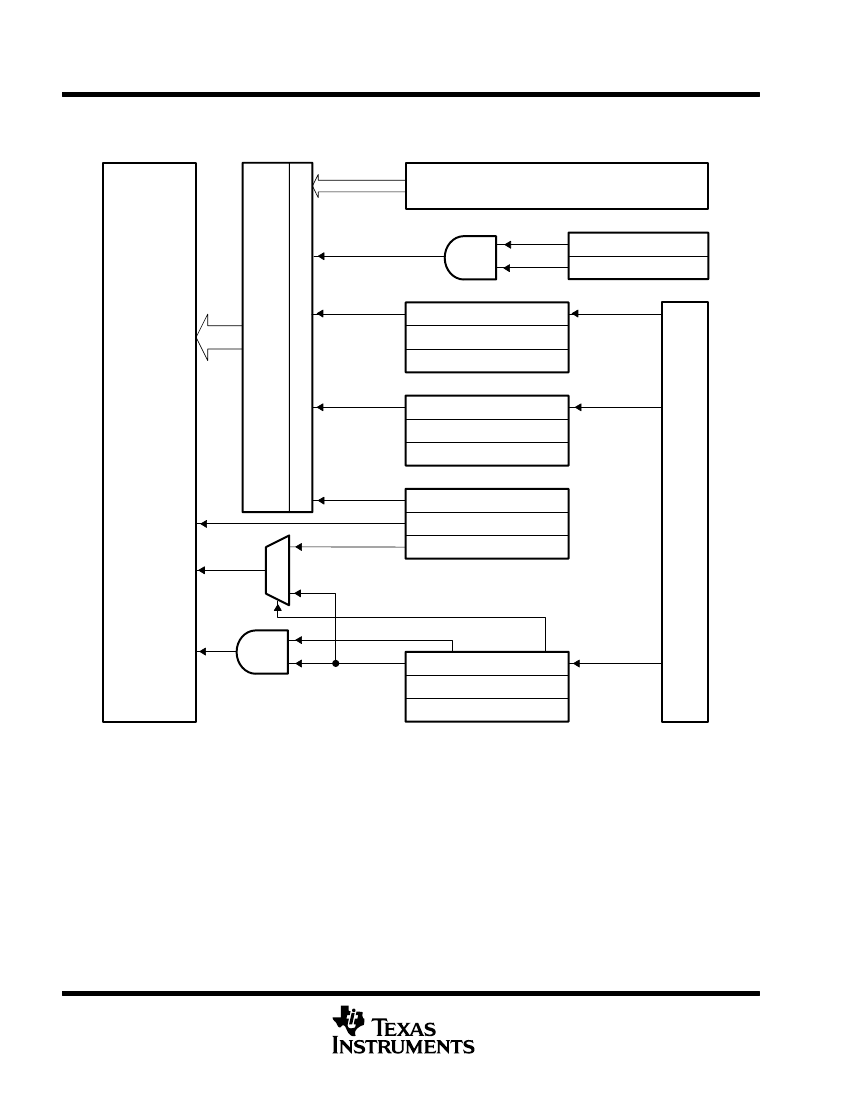

Figure 5 shows how the various interrupt sources are multiplexed within the F2810 and F2812 devices.

Peripherals (SPI, SCI, McBSP, CAN, EV, ADC)

(41 Interrupts)

WAKEINT

WDINT

LPMINT

Watchdog

Low-Power Modes

XINT1

96 Interrupts鈥?/div>

Interrupt Control

XINT1CR(15:0)

XINT1CTR(15:0)

INT1 to INT12

PIE

Interrupt Control

XINT2

PRODUCT PREVIEW

C28x CPU

XINT2CR(15:0)

XINT2CTR(15:0)

GPIO

MUX

TINT0

INT14

MUX

TINT2

TINT1

INT13

TIMER 0

TIMER 2 (for RTOS)

TIMER 1 (for RTOS)

select

enable

NMI

Interrupt Control

XNMICR(15:0)

XNMICTR(15:0)

XNMI_XINT13

鈥?Out of a possible 96 interrupts, 45 are currently used by peripherals.

Figure 5. Interrupt Sources

34

POST OFFICE BOX 1443

鈥?/div>

HOUSTON, TEXAS 77251鈥?443