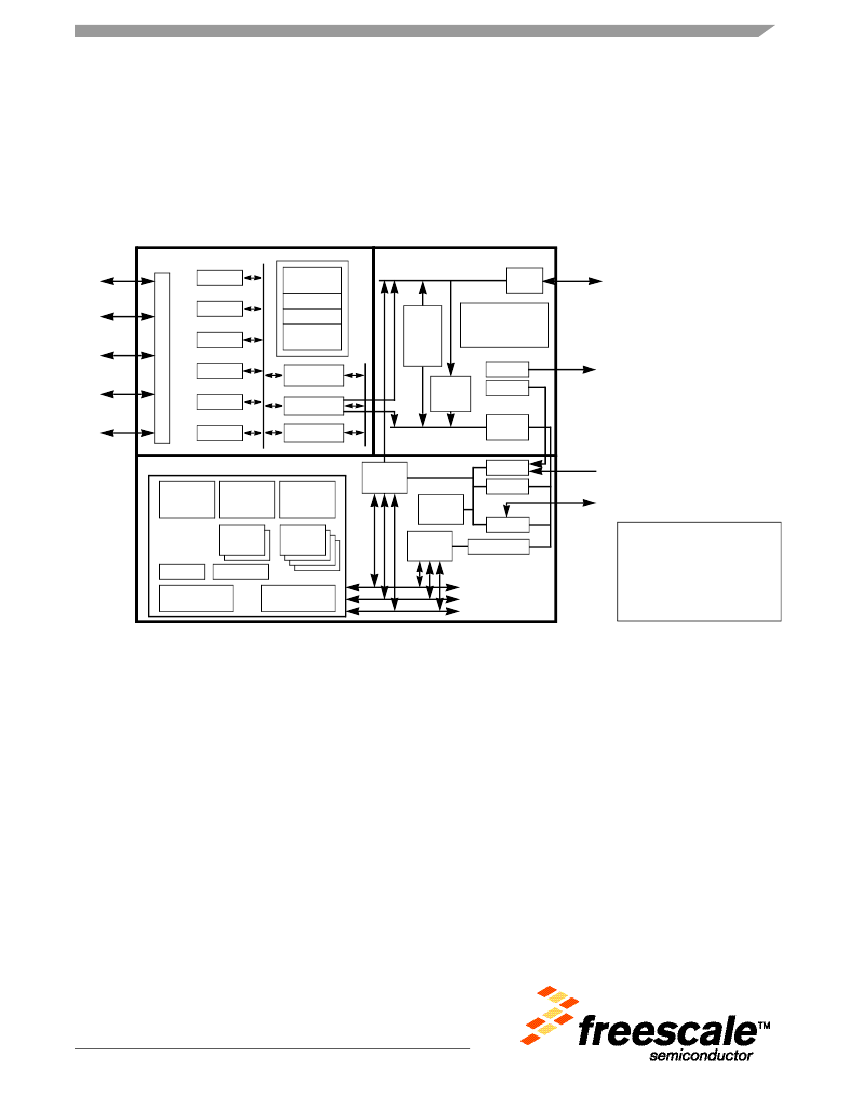

EOnCE鈩?/div>

Clock/PLL

Data ALU

Register

File

Data

ALU

Q2PPC

Bridge

Serial Interface and TSA

The Freescale MSC8101

16-bit DSP is the first

member of the family of

DSPs based on the

StarCore SC140 DSP core.

The MSC8101 is available

in three core speed levels:

250, 275, and 300 MHz.

128-bit QBus

PIC

Interrupts

EFCOP

8/16-bit

Host

Interface

Boot

ROM

HDI16

SRAM

512 KB

L1 Interface

What鈥檚 New?

Rev. 16 includes the following

changes:

鈥?Changed most

REFCLK

references to

DLLIN

in

Section 2.7.4.

Power

Management

128-bit P-Bus

64-bit XA Data Bus

64-bit XB Data Bus

Figure 1.

MSC8101 Block Diagram

The Freescale MSC8101 DSP is a very versatile device that integrates the high-performance SC140 four-ALU (arithmetic

logic unit) DSP core along with 512 KB of internal memory, a communications processor module (CPM), a 64-bit bus, a very

flexible System Integration Unit (SIU), and a 16-channel DMA engine on a single device. With its four-ALU core, the

MSC8101 can execute up to four multiply-accumulate (MAC) operations in a single clock cycle. The MSC8101 CPM is a 32-

bit RISC-based communications protocol engine that can network to time-division multiplexed (TDM) highways, Ethernet,

and asynchronous transfer mode (ATM) backbones. The MSC8101 60x-compatible bus interface facilitates its connection to

multi-master system architectures. The very large internal memory, 512 KB, reduces the need for external program and data

memories. The MSC8101 offers 1500 DSP MMACS (1200 core and 300 EFCOP) performance using an internal 300 MHz

clock with a 1.6 V core and independent 3.3 V input/output (I/O).

漏 Freescale Semiconductor, Inc., 2001, 2004. All rights reserved.