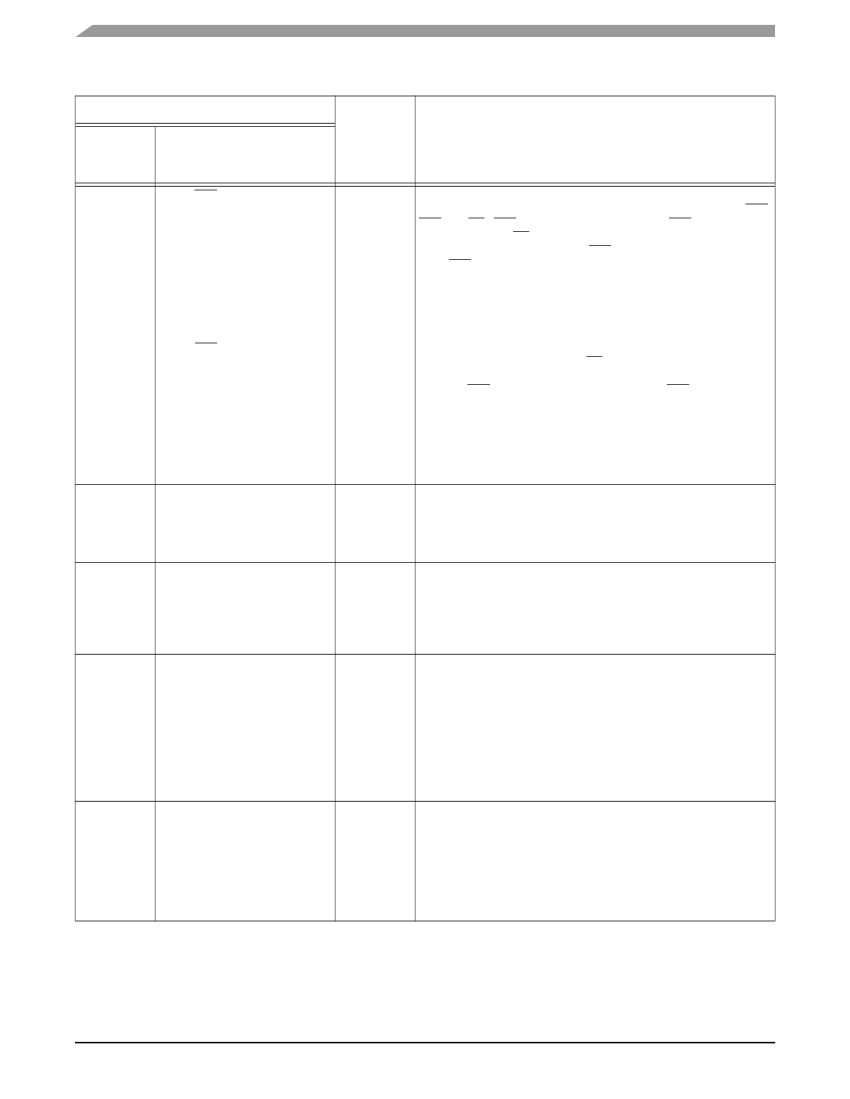

Signals/Connections

Table 1-8.

Name

General-

Purpose I/O

PB28

Port B Signals (Continued)

Peripheral Controller:

Dedicated I/O

Protocol

FCC2: RTS

HDLC serial, HDLC nibble,

and

transparent

Dedicated

I/O Data

Direction

Output

Description

FCC2: Request to Send

One of the standard modem interface signals supported by FCC2 (RTS,

CTS, and CD). RTS is asynchronous with the data. RTS is typically used

in conjunction with CD. The MSC8101 FCC2 transmitter requests the

receiver to send data by asserting RTS low. The request is accepted

when CTS is returned low.

FCC2: Media Independent Interface Receive Error

Asserted by an external fast Ethernet PHY to indicate a receive error,

which often indicates bad wiring.

SCC2: Request to Send, Transmit Enable

Typically used in conjunction with CD supported by SCC2. The

MSC8101 SCC2 transmitter requests the receiver to send data by

asserting RTS low. The request is accepted when CTS is returned low.

TENA is the signal used in Ethernet mode.

Time-Division Multiplexing B2: Layer 1 Transmit Synchronization

The synchronizing signal for the transmit channel. See the serial

interface with time-slot assigner chapter in the

MSC8101 Reference

Manual.

FCC2: Media Independent Interface Collision Detect

Asserted by an external fast Ethernet PHY when a collision is detected.

Time-Division Multiplexing C2: Layer 1 Transmit Data

TDMC2 transmits serial data out of L1TXD.

FCC2: Media Independent Interface Carrier Sense Input

Asserted by an external fast Ethernet PHY to indicate activity on the

cable.

Time-Division Multiplexing C2: Layer 1 Receive Data

TDMC2 receives serial data from L1RXD.

FCC2: MII and HDLC Nibble Transmit Data Bit 3

TXD3 is bit 3 and the most significant bit of the transmit data nibble.

Time-Division Multiplexing A1: Nibble Layer 1 Transmit Data Bit 3

L1TXD3 is bit 3 and the most significant bit of the transmit data nibble.

Time-Division Multiplexing C2: Layer 1 Transmit Synchronization

The synchronizing signal for the transmit channel. See the

Serial

Interface with Time-Slot Assigner

chapter in the

MSC8101 Reference

Manual.

FCC2: MII and HDLC Nibble: Transmit Data Bit 2

TXD2 is bit 2 of the transmit data nibble.

Time-Division Multiplexing A1: Nibble Layer 1 Receive Data Bit 3

L1RXD3 is bit 3 and the most significant bit of the receive data nibble.

Time-Division Multiplexing C2: Layer 1 Receive Synchronization

The synchronizing signal for the receive channel.

FCC2: RX_ER

MII

Input

SCC2: RTS, TENA

Output

SI2 TDMB2: L1TSYNC

TDM serial

Input

PB27

FCC2: COL

MII

SI2 TDMC2: L1TXD

TDM serial

Input

Output

Input

PB26

FCC2: CRS

MII

SI2 TDMC2: L1RXD

TDM serial

PB25

FCC2: TXD3

MII

and

HDLC nibble

Input

Output

SI1 TDMA1: L1TXD3

TDM nibble

Output

SI2 TDMC2: L1TSYNC

TDM serial

PB24

FCC2: TXD2

MII

and

HDLC nibble

SI1 TDMA1: L1RXD3

nibble

SI2 TDMC2: L1RSYNC

serial

Input

Output

Input

Input

MSC8101 Technical Data, Rev. 16

1-22

Freescale Semiconductor