Physical and Electrical Specifications

2

This document contains detailed information on environmentatl limits, power considerations, DC/AC electrical

characteristics, and AC timing specifications for the MSC8101 communications processor, mask set 2K87M. For

additional information, see the

MSC8101 Reference Manual.

2.1 Absolute Maximum Ratings

CAUTION

This device contains circuitry protecting against damage due to

high static voltage or electrical fields; however, normal precautions

should be taken to avoid exceeding maximum voltage ratings.

Reliability is enhanced if unused inputs are tied to an appropriate

logic voltage level (for example, either GND or V

CC

).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another

specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation

of process parameter values in one direction. The minimum specification is calculated using the worst case for the

same parameters in the opposite direction. Therefore, a 鈥渕aximum鈥?value for a specification never occurs in the

same device with a 鈥渕inimum鈥?value for another specification; adding a maximum to a minimum represents a

condition that can never exist.

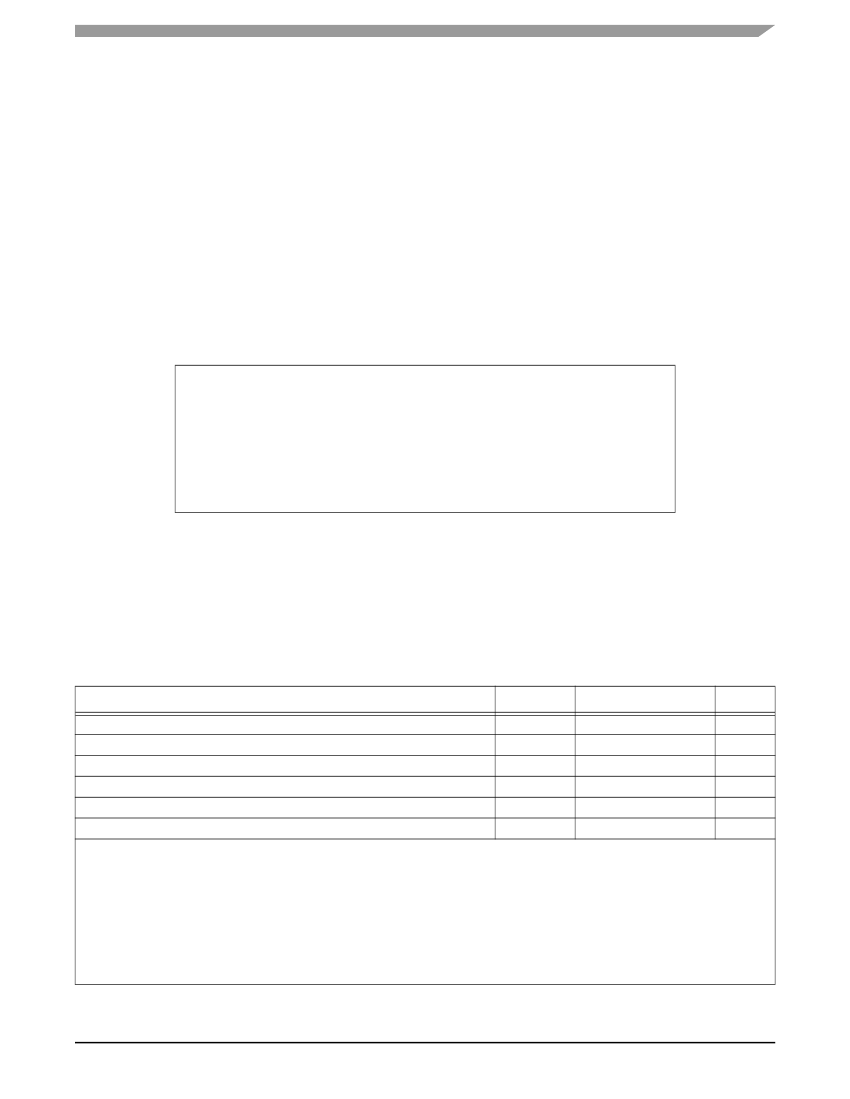

Table 2-1

describes the maximum electrical ratings for the MSC8101.

Table 2-1.

Rating

Core supply voltage

3

PLL supply voltage

3

I/O supply voltage

3

Input voltage

3

Maximum operating temperature range

4

Storage temperature range

Notes:

1.

2.

3.

Absolute Maximum Ratings

2

Symbol

V

DD

V

CCSYN

V

DDH

V

IN

T

J

T

STG

Value

鈥?.2 to 1.7

鈥?.2 to 1.7

鈥?.2 to 3.6

(GND 鈥?0.2) to 3.6

鈥?0 to 120

鈥?5 to +150

Unit

V

V

V

V

掳C

掳C

4.

Functional operating conditions are given in

Table 2-2.

Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond

the listed limits may affect device reliability or cause permanent damage.

The input voltage must not exceed the I/O supply V

DDH

by more than 2.5 V at any time, including during power-on reset. In

turn, V

DDH

can exceed V

DD

/V

CCSYN

by more than 3.3 V during power-on reset, but for no more than 100 ms. V

DDH

should not

exceed V

DD

/V

CCSYN

by more than 2.1 V during normal operation. V

DD

/V

CCSYN

must not exceed V

DDH

by more than 0.4 V at

any time, including during power-on reset. See

Section 4.2,

Electrical Design Considerations,

on page 4-1 for more

information.

Section 4.1,

Thermal Design Considerations,

on page 4-1 includes a formula for computing the chip junction temperature

(T

J

).

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

2-1