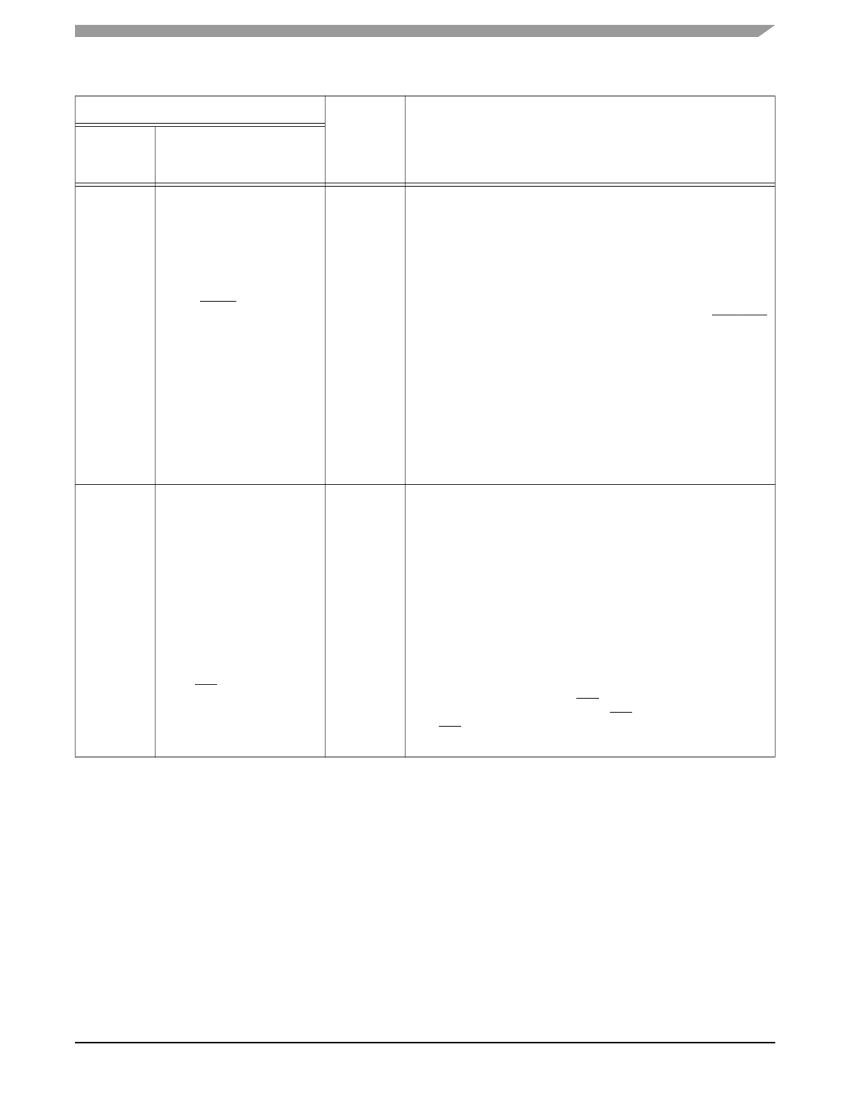

CPM Ports

Table 1-9.

Name

General-

Purpose I/O

PC30

Port C Signals (Continued)

Peripheral Controller:

Dedicated I/O

Protocol

BRG2O

Dedicated

I/O Data

Direction

Output

Description

Baud-Rate Generator 2 Output

The CPM supports up to 8 BRGs used internally by the bank-of-clocks

selection logic and/or to provide an output to one of the 8 BRG pins.

Clock 2

The CPM supports up to 10 clock input pins sent to the bank-of-clocks

selection logic, where they can be routed to the controllers.

Timer 1: Timer Out 1

The timers (Timer[1鈥?]) can output a signal on a timer output (TOUT[1鈥?])

when the reference value is reached. This signal can be an active-low

pulse or a toggle of the current output. The output can also connect

internally to the input of another timer, resulting in a 32-bit timer.

External Request 1

Asserts an internal request to the CPM processor. The signal can be

programmed as level- or edge-sensitive, and also has programmable

priority. Refer to the RISC Controller Configuration Register (RCCR)

description in the Chapter 17 of the

MSC8101 Reference Manual

for

programming information. There are no current microcode applications for

this request line. It is reserved for future development.

Baud-Rate Generator 3 Output

The CPM supports up to 8 BRGs used internally by the bank-of-clocks

selection logic and/or to provide an output to one of the 8 BRG pins.

Clock 3

The CPM supports up to 10 clock input pins sent to the bank-of-clocks

selection logic, where they can be routed to the controllers.

Timer Input 2

A timer can have one of the following sources: another timer, system

clock, system clock divided by 16 or a timer input. The CPM supports up to

4 timer inputs. The timer inputs can be captured on the rising, falling or

both edges.

SCC1: Clear to Send, Collision

Typically used in conjunction with RTS. The MSC8101 SCC1 transmitter

sends out a request to send data signal (RTS). The request is accepted

when CTS is returned low. CLSN is the signal used in Ethernet mode. See

also PC15.

CLK2

Input

Timer1: TOUT1

Output

EXT1

Input

PC29

BRG3O

Output

CLK3

Input

TIN2

Input

SCC1: CTS, CLSN

Input

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

1-25