Physical and Electrical Specifications

2.5 Clock Configuration

The following sections provide a general description of clock configuration.

2.5.1

Valid Clock Modes

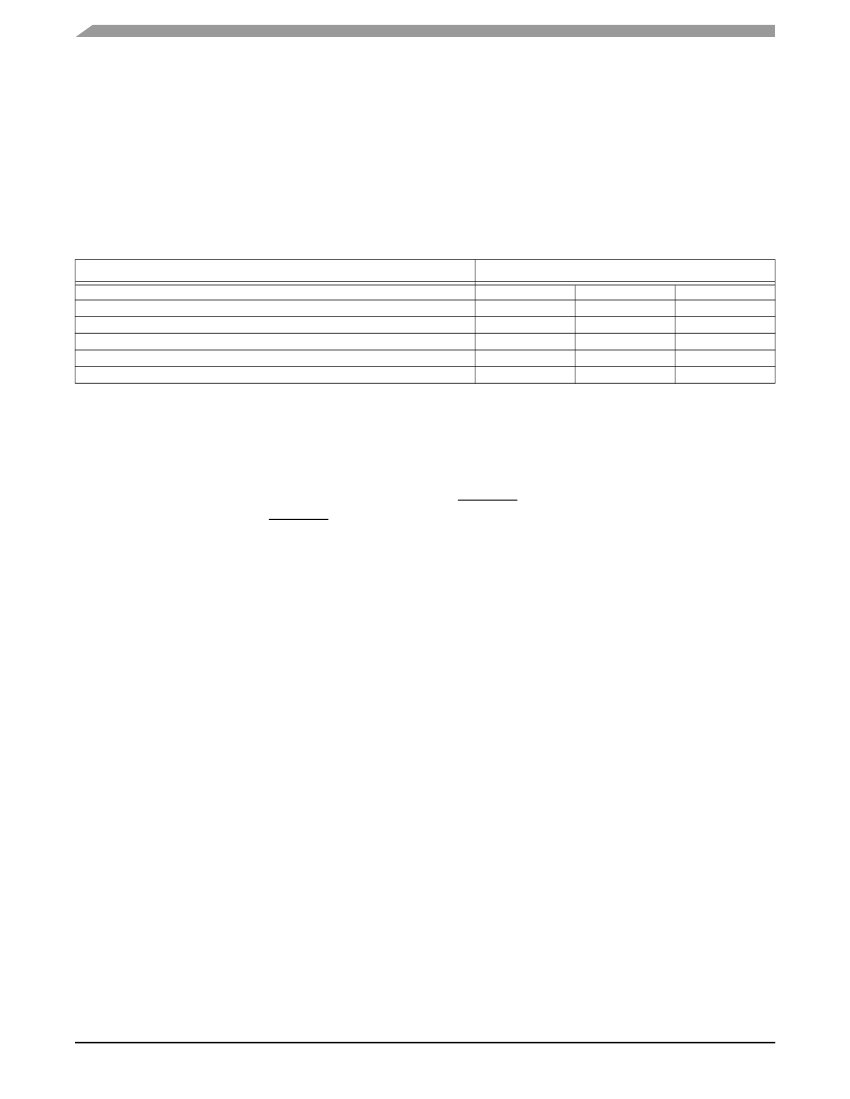

Table 2-6

shows the maximum frequency values for each rated core frequency (250, 275, or 300 MHz). The user

must ensure that maximum frequency values are not exceeded.

Table 2-6.

Characteristic

Core Frequency

CPM Frequency (CPMCLK)

Bus Frequency (BCLK)

Serial Communication Controller Clock Frequency (SCLK)

Baud Rate Generator Clock Frequency (BRGCLK)

External Clock Output Frequency (CLKOUT)

250

166.67

83.33

83.33

83.33

83.33

Maximum Frequencies

Maximum Frequency in MHz

275

183.33

91.67

91.67

91.67

91.67

300

200

100

100

100

100

Six bit values map the MSC8101 clocks to one of the valid configuration mode options. Each option determines the

CLKIN

, SC140, system bus, SCC clock, CPM, and

CLKOUT

frequencies. The six bit values are derived from three

dedicated input pins (

MODCK[1鈥?]

) and three bits from the hard reset configuration word (MODCK_H). To

configure the SPLL pre-division factor, SPLL multiplication factor, and the frequencies for the SC140, SCC

clocks, CPM parallel I/O ports, and system buses, the

MODCK[1鈥?]

pins are sampled and combined with the

MODCK_H values when the internal power-on reset (internal

PORESET

) is deasserted. Clock configuration

changes only when the internal

PORESET

signal is deasserted. The following factors are configured:

鈥?SPLL pre-division factor (SPLL PDF)

鈥?SPLL multiplication factor (SPLL MF)

鈥?Bus post-division factor (Bus DF)

鈥?CPM division factor (CPM DF)

鈥?Core division factor (Core DF)

鈥?CPLL pre-division factor (CPLL PDF)

鈥?CPLL multiplication factor (CPLL MF)

The SCC division factor (SCC DF) is fixed at 4. The BRG division factor (BRG DF) is configured through the

System Clock Control Register (SCCR) and can be 4, 16 (default after reset), 64, or 256.

Note:

Refer to

Clock Mode Selection for MSC8101 and MSC8103 Mask Set 2K87M

(AN2306) for details on

clock configuration.

2.5.2

Clocks Programming Model

This section describes the clock registers in detail. The registers discussed are as follows:

鈥?System Clock Control Register (SCCR)

鈥?System Clock Mode Register (SCMR)

MSC8101 Technical Data, Rev. 16

2-4

Freescale Semiconductor