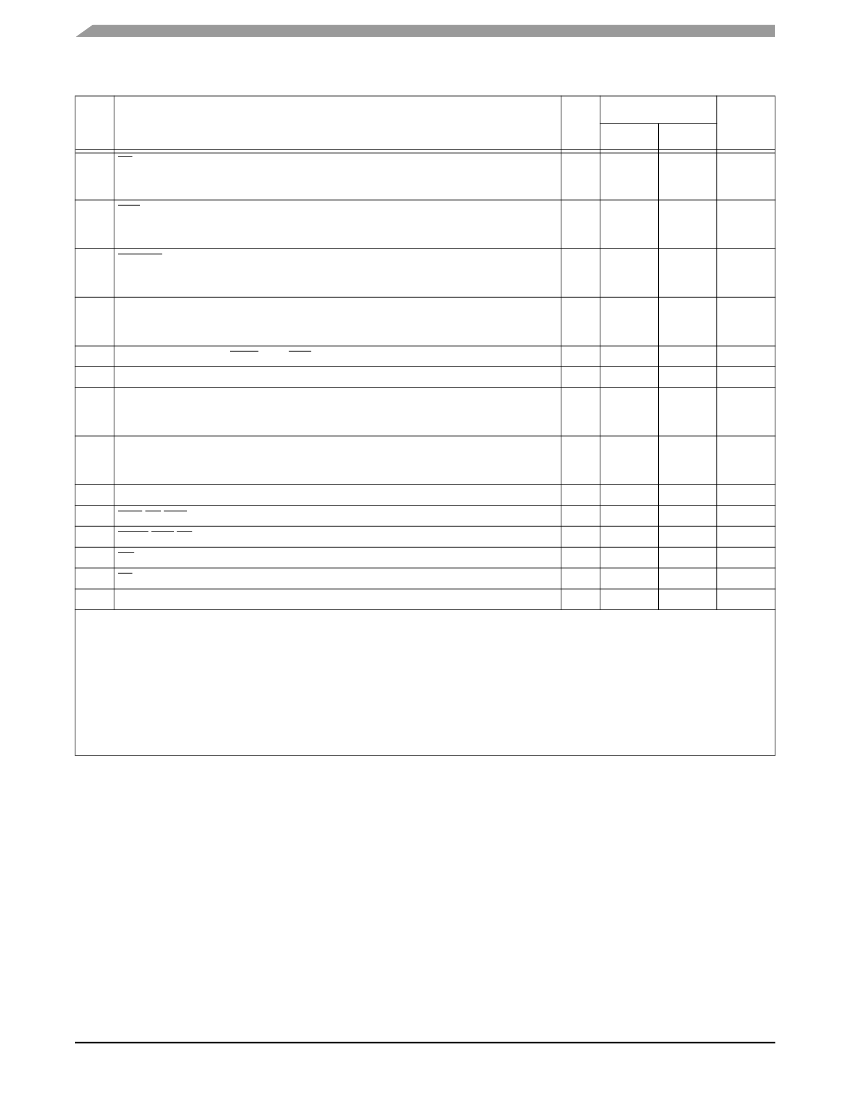

Physical and Electrical Specifications

Table 2-17.

No.

31a

AC Timing for SIU Outputs

Maximum

2

Min.

30 pF

50 pF

6.5

5.5

4.5

5.0

5.5

5.0

7.8

7.0

7.0

5.0

6.5

7.5

5.5

8.0

7.0

5.5

6.0

5.5

5.0

6.0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Characteristic

TA delay from the 50% level of the DLLIN rising edge

鈥?Pipeline mode

鈥?Non-pipeline mode

TEA delay from the 50% level of the DLLIN rising edge

鈥?Pipeline mode

鈥?Non-pipeline mode

PSDVAL delay from the 50% level of the DLLIN rising edge

鈥?Pipeline mode

鈥?Non-pipeline mode

Address bus delay from the 50% level of the DLLIN rising edge

鈥?Multi master mode (SIUBCR[EBM] = 1)

鈥?Single master mode (SIUBCR[EBM] = 0)

Address attributes: TT/TBST/TSIZ/GBL delay from the 50% level of the DLLIN rising edge

BADDR delay from the 50% level of the DLLIN rising edge

Data bus delay from the 50% level of the DLLIN rising edge

鈥?Pipeline mode

鈥?Non-pipeline mode

DP delay from the 50% level of the DLLIN rising edge

鈥?Pipeline mode

鈥?Non-pipeline mode

Memory controller signals/ALE delay from the 50% level of the DLLIN rising edge

DBG/BR/DBB delay from the 50% level of the DLLIN rising edge

AACK/ABB/CS delay from the 50% level of the DLLIN rising edge

BG delay from the 50% level of the DLLIN rising edge

TS delay from the 50% level of the DLLIN rising edge

Delay from the 50% level of the DLLIN rising edge for all other signals

1.

Units

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

1.0

5.0

4.0

3.0

3.5

4.0

3.5

6.3

5.5

5.5

3.5

5.0

6.0

4.0

6.5

5.5

4.0

4.5

4.0

3.5

4.5

31b

31c

32a

32b

32c

33a

33b

34

35a

35b

35c

35d

36

Notes:

2.

The maximum bus frequency depends on the mode:

鈥?In 60x-compatible mode connected to another MSC8101 device, the frequency is determined by adding the input and output

longest timing values, which results in a frequency of 75 MHz for 30 pF output capacitance. In multi-master mode when

connected to another MSC8101 device, the frequency is determined by adding the input and output longest timing values,

which results in a frequency of 75 MHz for 30 pF output capacitance.

鈥?Certain bus modes, such as non-extra cycle (EXDD = 1), non-pipelined, and ECC/Parity modes, result in slower bus

frequencies.

鈥?In single-master mode, the frequency depends on the timing of the devices connected to the MSC8101.

Output specifications are measured from the 50% level of the rising edge of DLLIN to the 50% level of the signal. Timings are

measured at the pin.

MSC8101 Technical Data, Rev. 16

2-14

Freescale Semiconductor