AC Timings

DLLIN

23

22

PIO/TIMER/DMA inputs

42

PIO/TIMER/DMA outputs

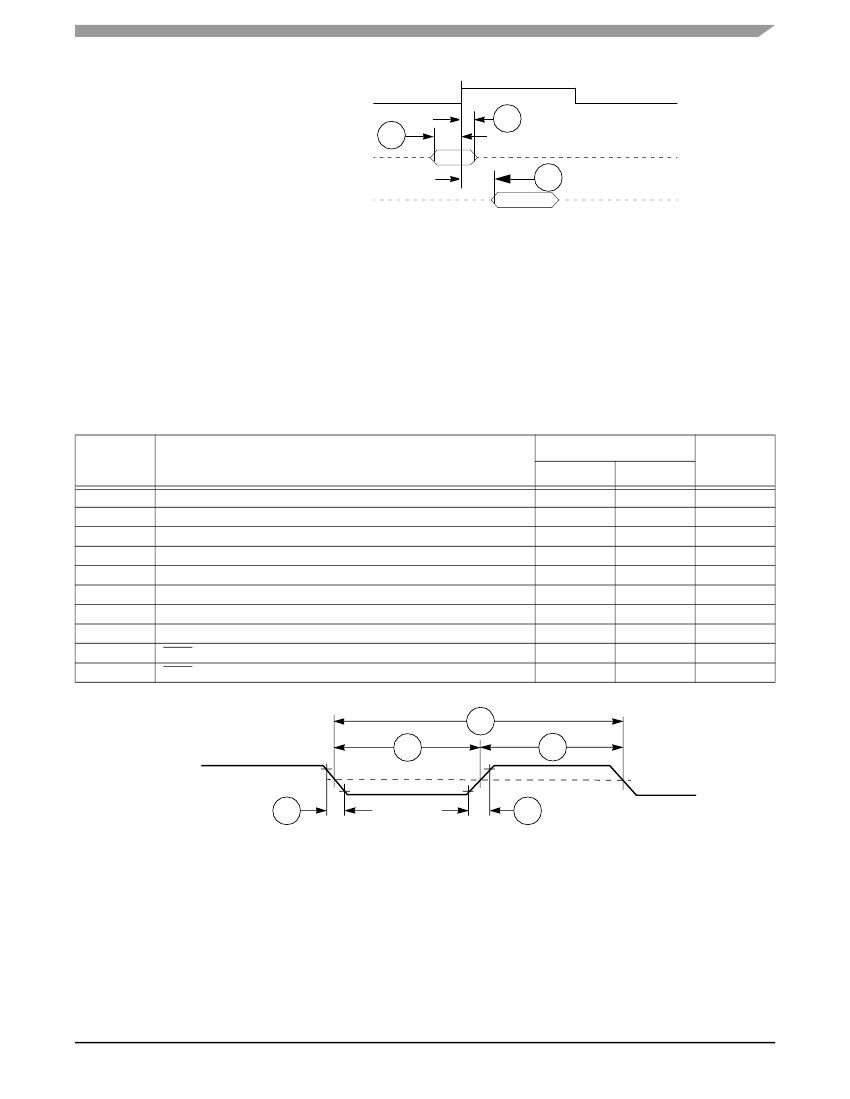

Figure 2-19.

PIO, Timer, and DMA Signal Diagram

Note:

The timing values refer to minimum system timing requirements. Actual implementation requires

conformance to the specific protocol requirements. Refer to

Chapter 1

to identify the specific input and

output signals associated with the referenced internal controllers and supported communication protocols.

For example, FCC1 supports ATM/Utopia operation in slave mode, multi-PHY master direct polling

mode, and multi-PHY master multiplexed polling mode and each of these modes supports its own set of

signals; the direction (input or output) of some of the shared signal names depends on the selected mode.

2.6.7

JTAG Signals

Table 2-22.

JTAG Timing

All frequencies

Unit

Min

Max

40.0

鈥?/div>

鈥?/div>

3.0

鈥?/div>

鈥?/div>

15.0

20.0

鈥?/div>

鈥?/div>

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

0.0

25.0

12.5

0.0

6.0

3.0

0.0

0.0

100.0

40.0

No.

500

501

502

503

508

509

510

511

512

513

TCK frequency of operation

TCK cycle time

Characteristics

TCK clock pulse width measured at 1.6 V

TCK rise and fall times

TMS, TDI data set-up time

TMS, TDI data hold time

TCK low to TDO data valid

TCK low to TDO high impedance

TRST assert time

TRST set-up time to TCK low

501

502

TCK

(Input)

V

IH

503

V

M

V

IL

503

502

V

M

Figure 2-20.

Test Clock Input Timing Diagram

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

2-23

MSC8101 PDF文件相关型号

MSC8101D

MSC8101相关型号PDF文件下载

-

型号

版本

描述

厂商

下载

-

英文版

Advanced Semiconductor [HIGH POWER GaAs FET]

ASI

-

英文版

Advanced Semiconductor [HIGH POWER GaAs FET]

ASI

-

英文版

Silicon Errata for the MSC8101 Processor, Mask 0K40A

FREESCALE

-

英文版

Networking Digital Signal Processor

-

英文版

MSC8102 Technical Data

-

英文版

Network-Ready DSP

-

英文版

MSC8112 Data Sheet

-

英文版

MSC8113 Data Sheet

-

英文版

MSC8122 Technical Data Sheeet

-

英文版

MSC8126 Technical Data Sheet

-

英文版

MSC8144 Quad Core Digital Signal Processor Data Sheet

-

英文版

MSC8151 Data Sheet

-

英文版

MSC8152 Data Sheet

-

英文版

MSC8154 Data Sheet

-

英文版

MSC8156 Data Sheet

-

英文版

Advanced Power Technology [RF & MICROWAVE TRANSISTORS G...

ADPOW

-

英文版

NPN RF TRANSISTOR

ASI

-

英文版

NPN RF TRANSISTOR

ASI [Advan...

-

英文版

RF & MICROWAVE TRANSISTORS GENERAL PURPOSE LINEAR APPLICATIO...

-

英文版

RF & MICROWAVE TRANSISTORS GENERAL PURPOSE LINEAR APPLICATIO...

STMICROELECTRON...