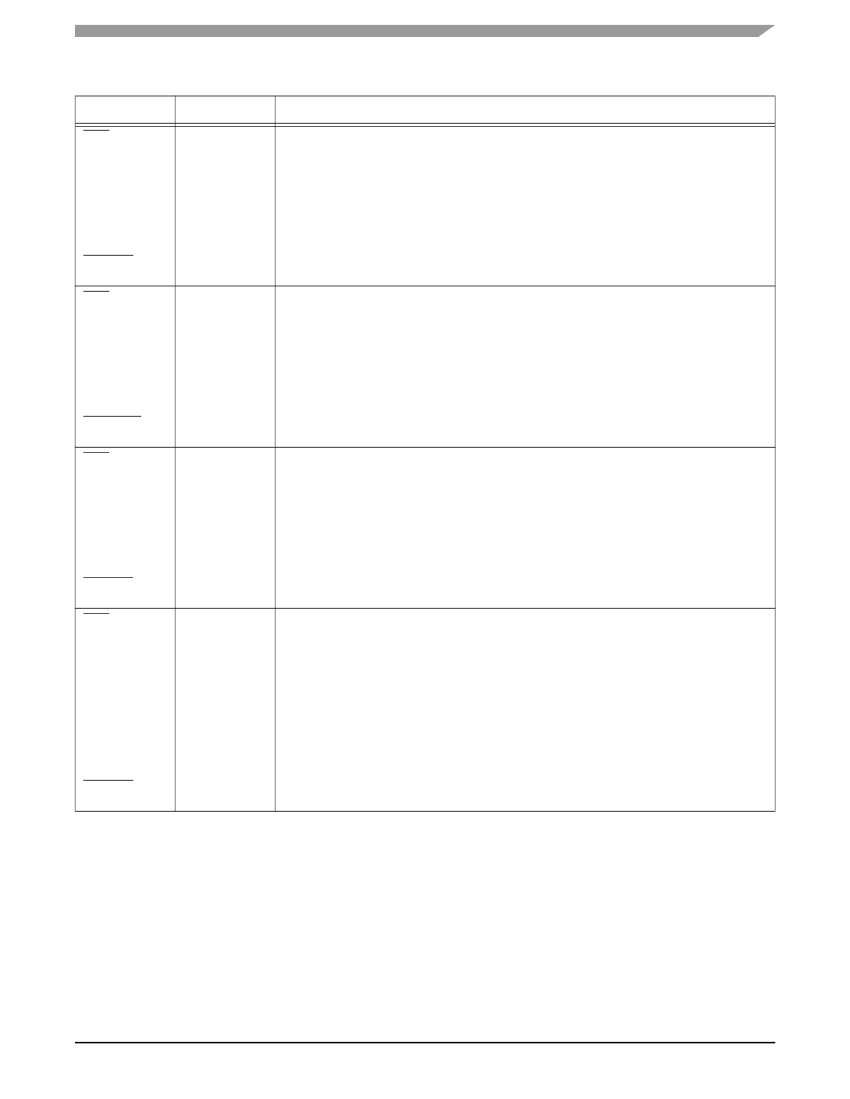

System Bus, HDI16, and Interrupt Signals

Table 1-5.

Signal

IRQ1

System Bus, HDI16, and Interrupt Signals (Continued)

Description

Interrupt Request 1

1

One of eight external lines that can request a service routine, via the internal interrupt controller,

from the SC140 core.

Data Parity 1

1

The agent that drives the data bus also drives the data parity signals. The value driven on the data

parity one pin should give odd parity (odd number of ones) on the group of signals that includes data

parity 1 and D[8鈥?5].

External Bus Grant 2

1,2

The MSC8101 asserts this pin to grant bus ownership to an external bus master.

Interrupt Request 2

1

One of eight external lines that can request a service routine, via the internal interrupt controller,

from the SC140 core.

Data Parity 2

1

The agent that drives the data bus also drives the data parity signals. The value driven on the data

parity two pin should give odd parity (odd number of ones) on the group of signals that includes data

parity 2 and D[16鈥?3].

External Data Bus Grant 2

1,2

The MSC8101 asserts this pin to grant data bus ownership to an external bus master.

Interrupt Request 3

1

One of eight external lines that can request a service routine, via the internal interrupt controller,

from the SC140 core.

Data Parity 3

1

The agent that drives the data bus also drives the data parity signals. The value driven on the data

parity three pin should give odd parity (odd number of ones) on the group of signals that includes

data parity 3 and D[24鈥?1].

External Bus Request 3

1,2

An external master asserts this pin to request bus ownership from the internal arbiter.

Interrupt Request 4

1

One of eight external lines that can request a service routine, via the internal interrupt controller,

from the SC140 core.

Data Parity 4

1

The agent that drives the data bus also drives the data parity signals. The value driven on the data

parity four pin should give odd parity (odd number of ones) on the group of signals that includes data

parity 4 and D[32鈥?9].

DMA Request 3

1

An external peripheral uses this pin to request DMA service.

External Bus Grant 3

1,2

The MSC8101 asserts this pin to grant bus ownership to an external bus master.

Data Flow

Input

DP1

Input/Output

EXT_BG2

IRQ2

Output

Input

DP2

Input/Output

EXT_DBG2

IRQ3

Output

Input

DP3

Input/Output

EXT_BR3

IRQ4

Input

Input

DP4

Input/Output

DREQ3

Input

EXT_BG3

Output

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

1-11