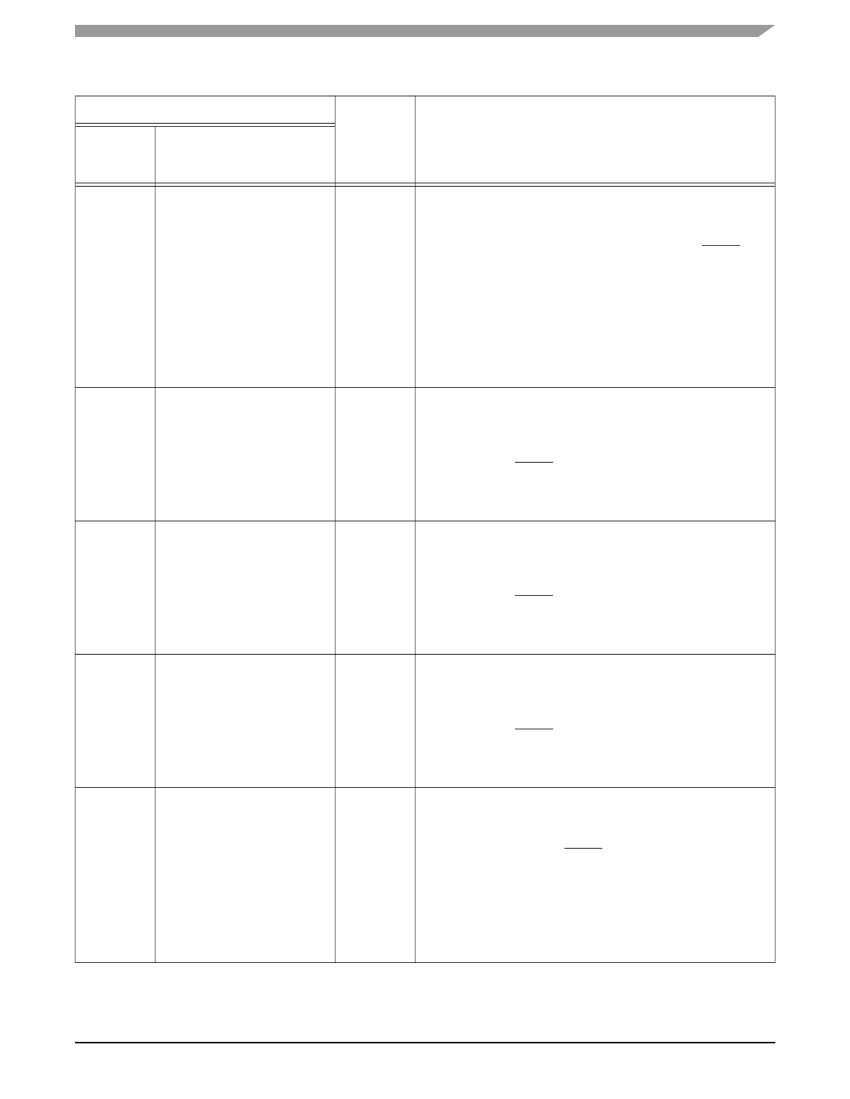

CPM Ports

Table 1-7.

Name

General-

Purpose I/O

PA17

Port A Signals (Continued)

Peripheral Controller:

Dedicated Signal

Protocol

FCC1: RXD7

UTOPIA

Dedicated

I/O Data

Direction

Input

Description

FCC1: UTOPIA Receive Data Bit 7.

The MSC8101 inputs ATM cell octets (UTOPIA interface data) on

RXD[0鈥?]. RXD7 is the most significant bit. When no ATM data is

available, idle cells are inserted. A cell is 53 bytes. To support Multi-PHY

configurations, RXD[0鈥?] is tri-stated, enabled only when RXENB is

asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 0

RXD[3鈥?] is supported by MII and HDLC nibble mode in FCC1. RXD0 is

the least significant bit.

FCC1: HDLC Serial and Transparent Receive Data Bit

This is the single receive data bit supported by HDLC and transparent

modes.

FCC1: UTOPIA Receive Data Bit 6.

The MSC8101 inputs ATM cell octets (UTOPIA interface data) on

RXD[0鈥?]. This is bit 6 of the receive data. RXD7 is the most significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes. To support Multi-PHY configurations, RXD[0鈥?] is tri-stated,

enabled only when RXENB is asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 1

This is bit 1 of the receive nibble data. RXD3 is the most significant bit.

FCC1: UTOPIA Receive Data Bit 5

The MSC8101 inputs ATM cell octets (UTOPIA interface data) on

RXD[0鈥?]. This is bit 5 of the receive data. RXD7 is the most significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes. To support Multi-PHY configurations, RXD[0鈥?] is tri-stated,

enabled only when RXENB is asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 2

This is bit 2 of the receive nibble data. RXD3 is the most significant bit.

FCC1: UTOPIA Receive Data Bit 4.

The MSC8101 inputs ATM cell octets (UTOPIA interface data) on

RXD[0鈥?]. RXD7 is the most significant bit. RXD0 is the least significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes. To support Multi-PHY configurations, RXD[0鈥?] is tri-stated,

enabled only when RXENB is asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 3

RXD3 is the most significant bit of the receive nibble bit.

FCC1: UTOPIA Receive Data Bit 3

The MSC8101 inputs ATM cell octets (UTOPIA interface data) on

RXD[0鈥?]. RXD7 is the most significant bit. RXD0 is the least significant

bit. A cell is 53 bytes. To support Multi-PHY configurations, RXD[0鈥?] is

tri-stated, enabled only when RXENB is asserted.

Module Serial Number Bit 2

The MSNUM has 6 bits that identify devices using the serial DMA

(SDMA) modules. MSNUM[0鈥?] is the sub-block code of the current

peripheral controller using SDMA. MSNUM5 indicates the section,

transmit (0) or receive (1), that is active during the transfer. The

information is recorded in the SDMA transfer error registers.

FCC1: RXD0

MII

and

HDLC nibble

Input

FCC1: RXD

HDLC serial

and

transparent

PA16

FCC1: RXD6

UTOPIA

Input

Input

FCC1: RXD1

MII

and

HDLC nibble

PA15

FCC1: RXD5

UTOPIA

Input

Input

RXD2

MII

and

HDLC nibble

PA14

FCC1: RXD4

UTOPIA

Input

Input

FCC1: RXD3

MII

and

HDLC nibble

PA13

FCC1: RXD3

UTOPIA

Input

Input

SDMA: MSNUM2

Output

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

1-19