Signals/Connections

1.1 Power Signals

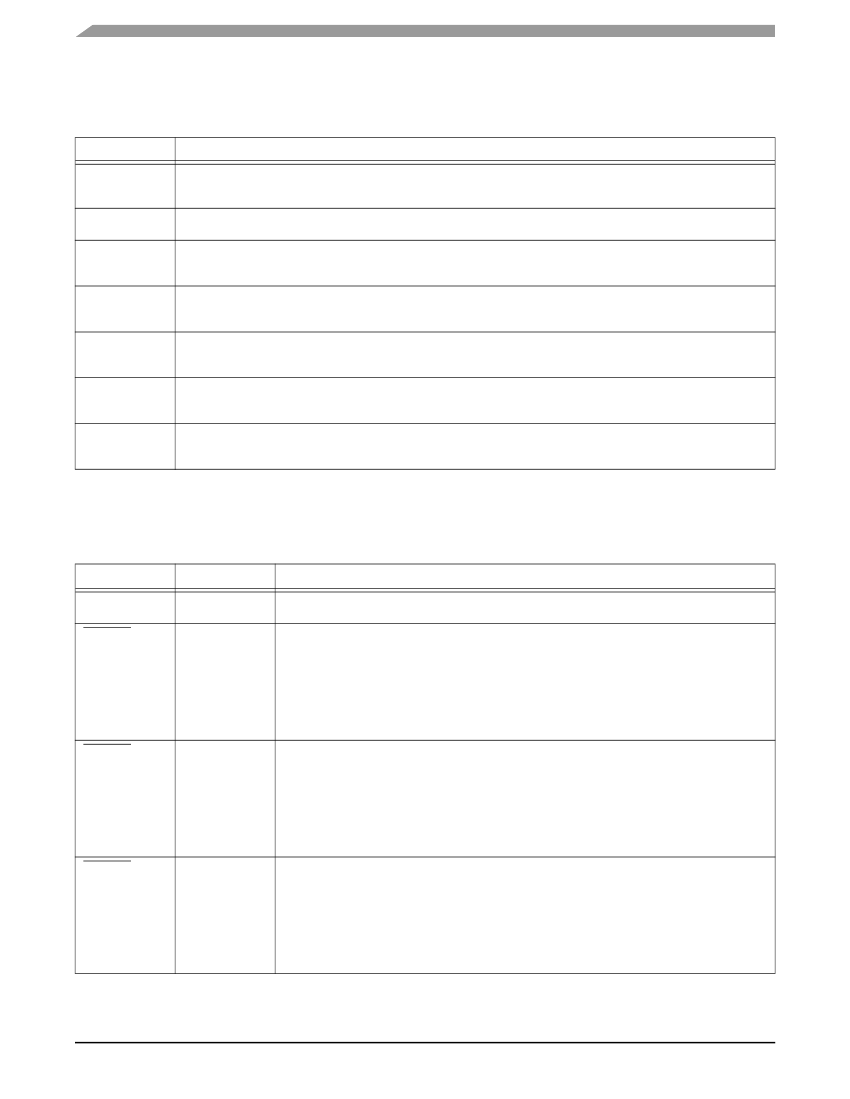

Table 1-2.

Power Name

V

DD

Power and Ground Signal Inputs

Description

Internal Logic Power

V

DD

dedicated for use with the device core. The voltage should be well-regulated and the input should be provided with

an extremely low impedance path to the V

DD

power rail.

Input/Output Power

This source supplies power for the I/O buffers. The user must provide adequate external decoupling capacitors.

System PLL Power

V

CC

dedicated for use with the system Phase Lock Loop (PLL). The voltage should be well-regulated and the input

should be provided with an extremely low impedance path to the V

CC

power rail.

SC140 PLL Power

V

CC

dedicated for use with the SC140 core PLL. The voltage should be well-regulated and the input should be provided

with an extremely low impedance path to the V

CC

power rail.

System Ground

An isolated ground for the internal processing logic. This connection must be tied externally to all chip ground

connections, except GND

SYN

and GND

SYN1

. The user must provide adequate external decoupling capacitors.

System PLL Ground

Ground dedicated for system PLL use. The connection should be provided with an extremely low-impedance path to

ground.

SC140 PLL Ground 1

Ground dedicated for SC140 core PLL use. The connection should be provided with an extremely low-impedance path

to ground.

V

DDH

V

CCSYN

V

CCSYN1

GND

GND

SYN

GND

SYN1

1.2 Clock Signals

Table 1-3.

Signal Name

CLKIN

MODCK1

Input

Input

Clock Signals

Signal Description

Type

Clock In

Primary clock input to the MSC8101 PLL.

Clock Mode Input 1

Defines the operating mode of internal clock circuits.

Transfer Code 0

Supplies information that can be useful for debugging bus transactions initiated by the MSC8101.

Bank Select 0

Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.

Clock Mode Input 2

Defines the operating mode of internal clock circuits.

Transfer Code 1

Supplies information that can be useful for debugging bus transactions initiated by the MSC8101.

Bank Select 1

Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.

Clock Mode Input 3

Defines the operating mode of internal clock circuits.

Transfer Code 2

Supplies information that can be useful for debugging bus transactions initiated by the MSC8101.

Bank Select 2

Selects the SDRAM bank when the MSC8101 is in 60x-compatible bus mode.

TC0

Output

BNKSEL0

MODCK2

Output

Input

TC1

Output

BNKSEL1

MODCK3

Output

Input

TC2

Output

BNKSEL2

Output

MSC8101 Technical Data, Rev. 16

1-4

Freescale Semiconductor