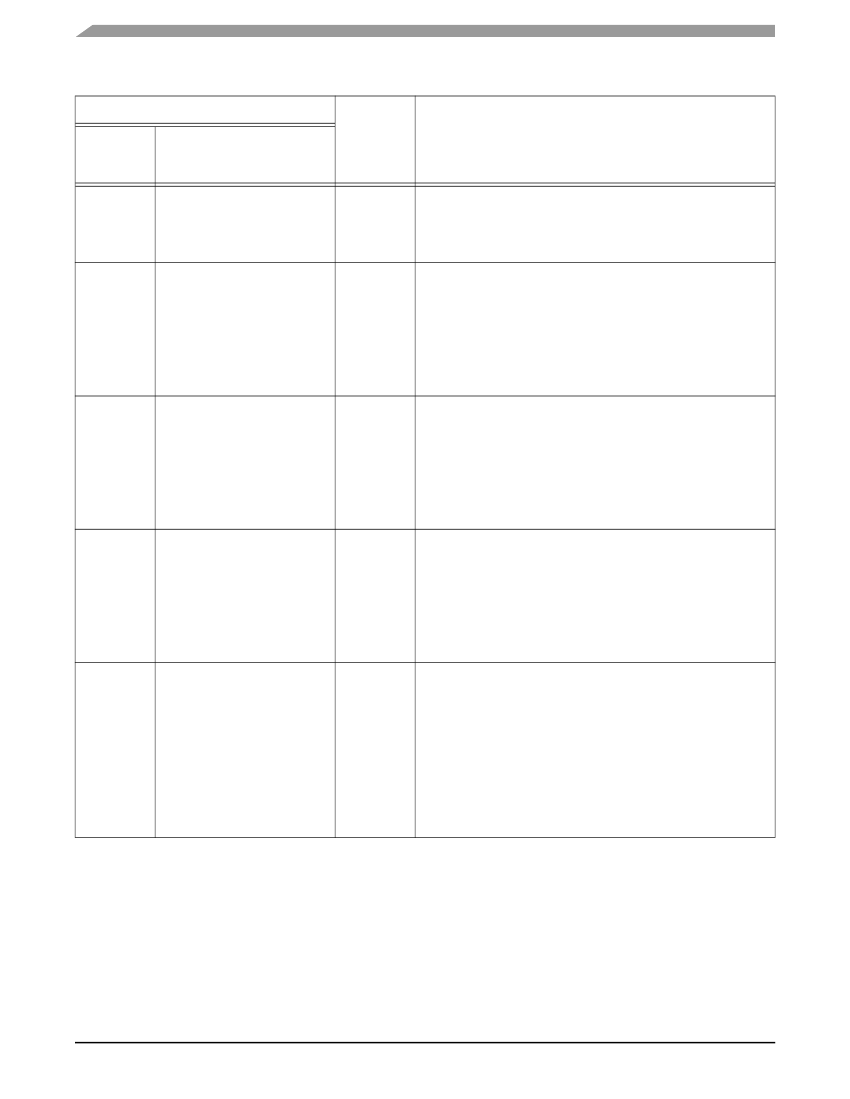

Signals/Connections

Table 1-7.

Name

General-

Purpose I/O

PA22

Port A Signals (Continued)

Peripheral Controller:

Dedicated Signal

Protocol

FCC1: TXD3

UTOPIA

Dedicated

I/O Data

Direction

Output

Description

FCC1: UTOPIA Transmit Data Bit 3

The MSC8101 outputs ATM cell octets (UTOPIA interface data) on

TXD[0鈥?]. This is bit 3 of the transmit data. TXD7 is the most significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes.

FCC1: UTOPIA Transmit Data Bit 4

The MSC8101 outputs ATM cell octets (UTOPIA interface data) on

TXD[0鈥?]. This is bit 4 of the transmit data. TXD7 is the most significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes.

FCC1: MII and HDLC Nibble Transmit Data Bit 3

TXD[3鈥?] supports MII and HDLC nibble modes in FCC1. TXD3 is the

most significant bit.

FCC1: UTOPIA Transmit Data Bit 5

The MSC8101 outputs ATM cell octets (UTOPIA interface data) on

TXD[0鈥?]. This is bit 5 of the transmit data. TXD7 is the most significant

bit. When no ATM data is available, idle cells are inserted. A cell is 53

bytes.

FCC1: MII and HDLC Nibble Transmit Data Bit 2

TXD[3鈥?] is supported by MII and HDLC nibble modes in FCC1. This is

bit 2 of the transmit data. TXD3 is the most significant bit.

FCC1: UTOPIA Transmit Data Bit 6

The MSC8101MSC8101 outputs ATM cell octets (UTOPIA interface

data) on TXD[0鈥?]. This is bit 6 of the transmit data. TXD7 is the most

significant bit. When no ATM data is available, idle cells are inserted. A

cell is 53 bytes.

FCC1: MII and HDLC Nibble Transmit Data Bit 1

TXD[3鈥?] is supported by MII and HDLC transparent nibble modes in

FCC1. This is bit 1 of the transmit data. TXD3 is the most significant bit.

FCC1: UTOPIA Transmit Data Bit 7.

The MSC8101 outputs ATM cell octets (UTOPIA interface data) on

TXD[0鈥?]. TXD7 is the most significant bit. When no ATM data is

available, idle cells are inserted. A cell is 53 bytes.

FCC1: MII and HDLC Nibble Transmit Data Bit 0

TXD[3鈥?] is supported by MII and HDLC nibble modes in FCC1. TXD0

is the least significant bit.

FCC1: HDLC Serial and Transparent Transmit Data Bit

This is the single transmit data bit in supported by HDLC serial and

transparent modes.

PA21

FCC1: TXD4

UTOPIA

Output

FCC1: TXD3

MII

and

HDLC nibble

PA20

FCC1: TXD5

UTOPIA

Output

Output

FCC1: TXD2

MII

and

HDLC nibble

PA19

FCC1: TXD6

UTOPIA

Output

Output

FCC1: TXD1

MII

and

HDLC nibble

PA18

FCC1: TXD7

UTOPIA

Output

Output

FCC1: TXD0

MII

and

HDLC nibble

Output

FCC1: TXD

HDLC serial

and

transparent

Output

MSC8101 Technical Data, Rev. 16

1-18

Freescale Semiconductor