and 鈥渃onfiguration slave.鈥?/div>

Directly after the deassertion of

PORESET

and choice of the reset operation mode as configuration master or

configuration slave, the MSC8101 starts the configuration process. The MSC8101 asserts

HRESET

and

SRESET

throughout the power-on reset process, including configuration. Configuration takes 1024

CLOCKIN

cycles, after

which

MODCK[1鈥?]

are sampled to determine the MSC8101鈥檚 working mode.

Next, the MSC8101 halts until the SPLL locks. The SPLL locks according to

MODCK[1鈥?]

, which are sampled, and

to MODCK_H taken from the Reset Configuration Word. SPLL locking time is 800 reference clocks, which is the

clock at the output of the SPLL Pre-divider. After the SPLL is locked, all the clocks to the MSC8101 are enabled.

If the DLLDIS bit in the reset configuration word is reset, the DLL starts the locking process after the SPLL is

locked. During PLL and DLL locking,

HRESET

and

SRESET

are asserted.

HRESET

remains asserted for another 512

BUS clocks and is then released. The

SRESET

is released three bus clocks later. If the DLLDIS bit in the reset

configuration word is set, the DLL is bypassed and there is no locking process, thus saving the DLL locking time.

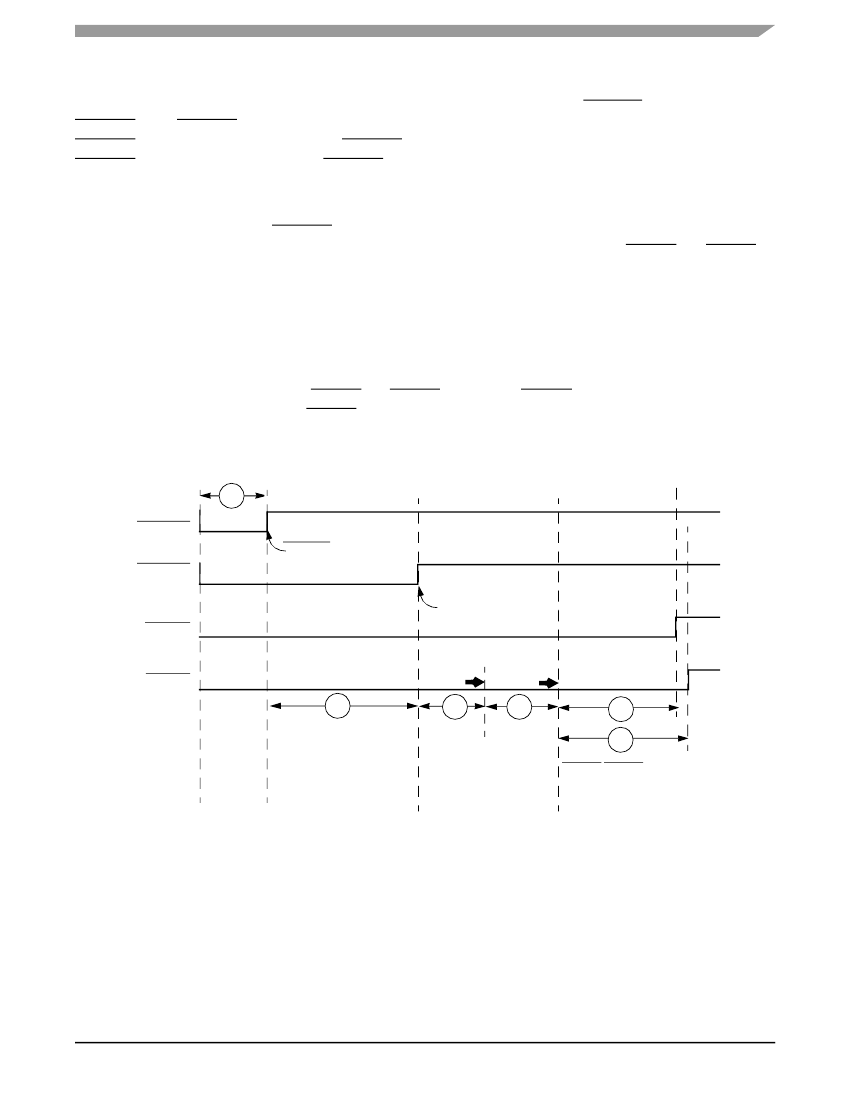

Figure 2-4

shows the power-on reset flow.

1

PORESET

Input

PORESET

Internal

asserted for

min 16

CLKIN.

RSTCONF is sampled for

master/slave determination

HRESET

Output (I/O)

MODCK[1鈥?] are sampled.

MODCK_H bits are ready

for PLL.

SRESET

Output (I/O)

2

In reset configuration mode:

reset configuration sequence

occurs in this period.

PLL locked

3

DLL locked

4

5

6

HRESET/SRESET are

extended for 512/515 bus

clocks, respectively, from PLL

and DLL Lock time.

PLL locks after

800 SPLLMFCLKs. DLL

locks 3073 bus clocks after

PLL is locked.

When DLL is disabled, reset

period is shortened by 3073

bus clocks.

Figure 2-4.

Hardware Reset Configuration Timing

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

2-11