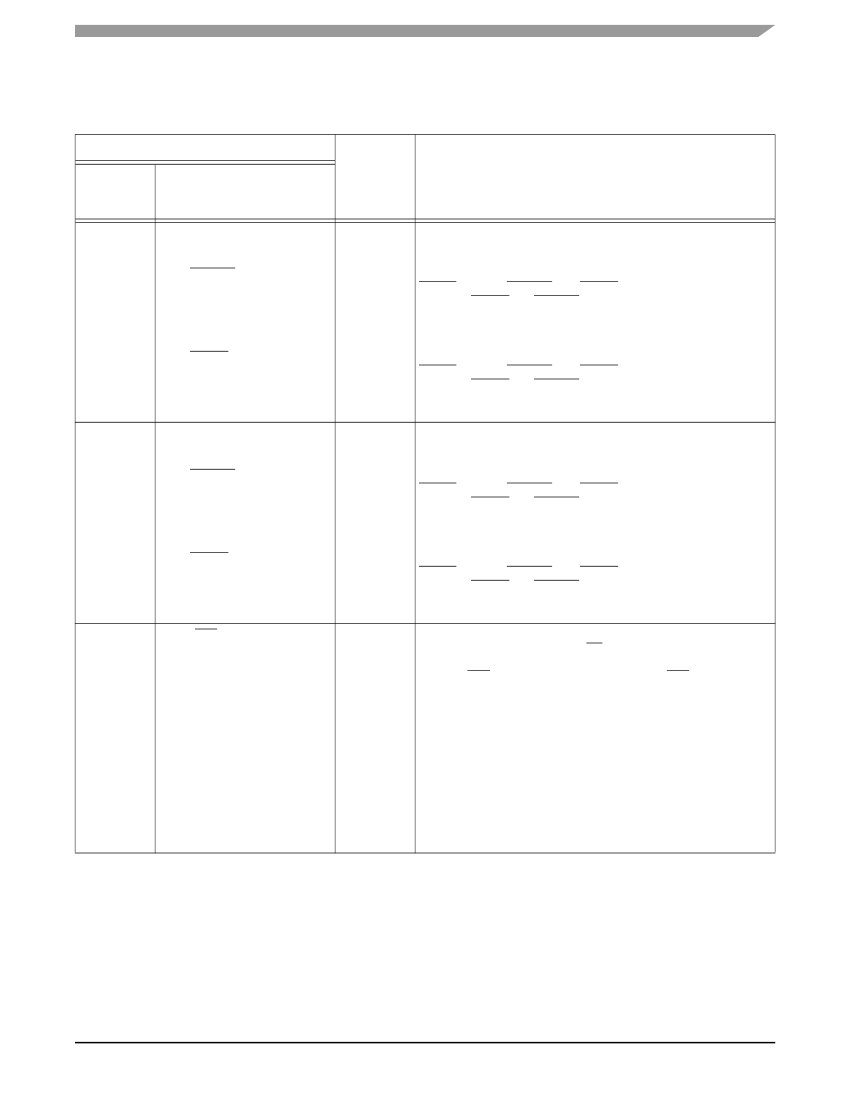

CPM Ports

1.6.4

Port D Signals

Table 1-10.

Name

Port D Signals

General-

Purpose I/O

PD31

Peripheral Controller:

Dedicated I/O

Protocol

SCC1: RXD

Dedicated

I/O Data

Direction

Input

Description

SCC1: Receive Data

SCC1 receives serial data from RXD.

DMA: Data Request Acknowledge 1

DACK1, DREQ1, DRACK1, and DONE1 belong to the SIU DMA

controller. DONE1 and DRACK1 are signals on the same pin and

therefore cannot be used simultaneously. There are two sets of DMA

pins associated with the PIO ports.

DMA: Done 1

DACK1, DREQ1, DRACK1, and DONE1 belong to the SIU DMA

controller. DONE1 and DRACK1 are signals on the same pin and

therefore cannot be used simultaneously. There are two sets of DMA

pins associated with the PIO ports.

SCC1: Transmit Data

SCC1 transmits serial data out of TXD.

DMA: Data Request Acknowledge 2

DACK2, DREQ2, DRACK2, and DONE2 belong to the SIU DMA

controller. DONE2 and DRACK2 are signals on the same pin and

therefore cannot be used simultaneously. There are two sets of DMA

pins associated with the PIO ports.

DMA: Done 2

DACK2, DREQ2, DRACK2, and DONE2 belong to the SIU DMA

controller. DONE2 and DRACK2 are signals on the same pin and

therefore cannot be used simultaneously. There are two sets of DMA

pins associated with the PIO ports.

SCC1: Request to Send, Transmit Enable

Typically used in conjunction with CD supported by SCC2. The

MSC8101 SCC1 transmitter requests the receiver to send data by

asserting RTS low. The request is accepted when CTS is returned low.

TENA is the signal used in Ethernet mode.

FCC1: UTOPIA Multi-PHY Master Receive Address Bit 3

This is master receive address bit 3.

FCC1: UTOPIA Slave Receive Address Bit 3

This is slave receive address bit 3.

FCC1: UTOPIA Multi-PHY Master Receive Cell Available 2 Direct

Polling

Asserted by an external PHY when one complete ATM cell is available

for transfer.

DMA: DRACK1

Output

DMA: DONE1

Input/ Output

PD30

SCC1: TXD

Output

DMA: DRACK2

Output

DMA: DONE2

Input/ Output

PD29

SCC1: RTS, TENA

Output

FCC1: RXADDR3

UTOPIA master

FCC1: RXADDR3

UTOPIA slave

FCC1: RXCLAV2

UTOPIA multi-PHY master, direct

polling

Output

Input

Input

MSC8101 Technical Data, Rev. 16

Freescale Semiconductor

1-33