Physical and Electrical Specifications

2.6.4

System Bus Access Timing

2.6.4.1 Core Data Transfers

Generally, all MSC8101 bus and system output signals are driven from the rising edge of the reference clock

(REFCLK), which is

DLLIN

. Memory controller signals, however, trigger on four points within a DLLIN cycle.

Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge of DLLIN (and

T3 at the falling edge), but the spacing of T2 and T4 depends on the PLL clock ratio selected, as

Table 2-15

shows.

Table 2-15.

Tick Spacing for Memory Controller Signals

Tick Spacing (T1 Occurs at the Rising Edge of DLLIN)

PLL Clock Ratio

T2

1:2, 1:3, 1:4, 1:5, 1:6

1:2.5

1:3.5

1/4 DLLIN

3/10 DLLIN

4/14 DLLIN

T3

1/2 DLLIN

1/2 DLLIN

1/2 DLLIN

T4

3/4 DLLIN

8/10 DLLIN

11/14 DLLIN

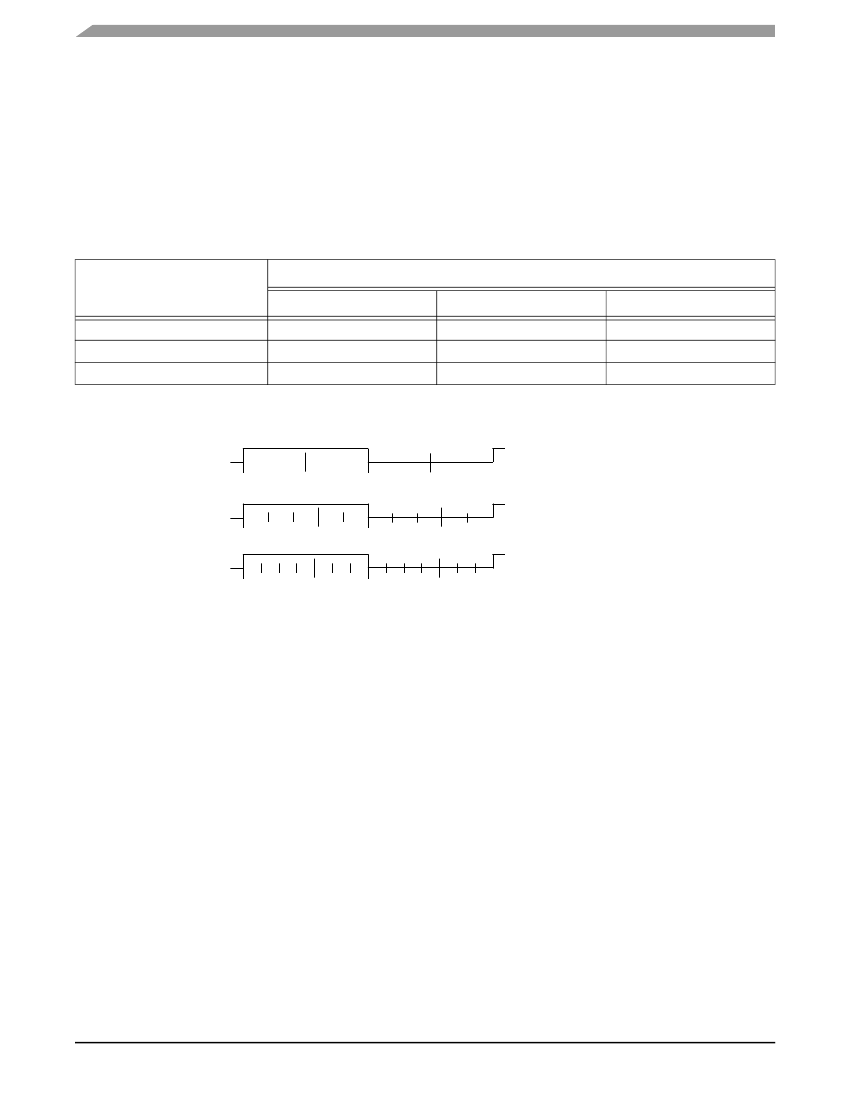

Figure 2-5

is a graphical representation of

Table 2-15.

DLLIN

T1

DLLIN

T1

DLLIN

T1

T2

T3

T4

T2

T3

T4

T2

T3

T4

for 1:2, 1:3, 1:4, 1:5, 1:6

for 1:2.5

for 1:3.5

Figure 2-5.

Internal Tick Spacing for Memory Controller Signals

Note:

The UPM machine and GPCM machine outputs change on the internal tick determined by the memory

controller programming; the AC specifications are relative to the internal tick. SDRAM machine outputs

change only on the

DLLIN

rising edge.

MSC8101 Technical Data, Rev. 16

2-12

Freescale Semiconductor