Design Considerations

GND

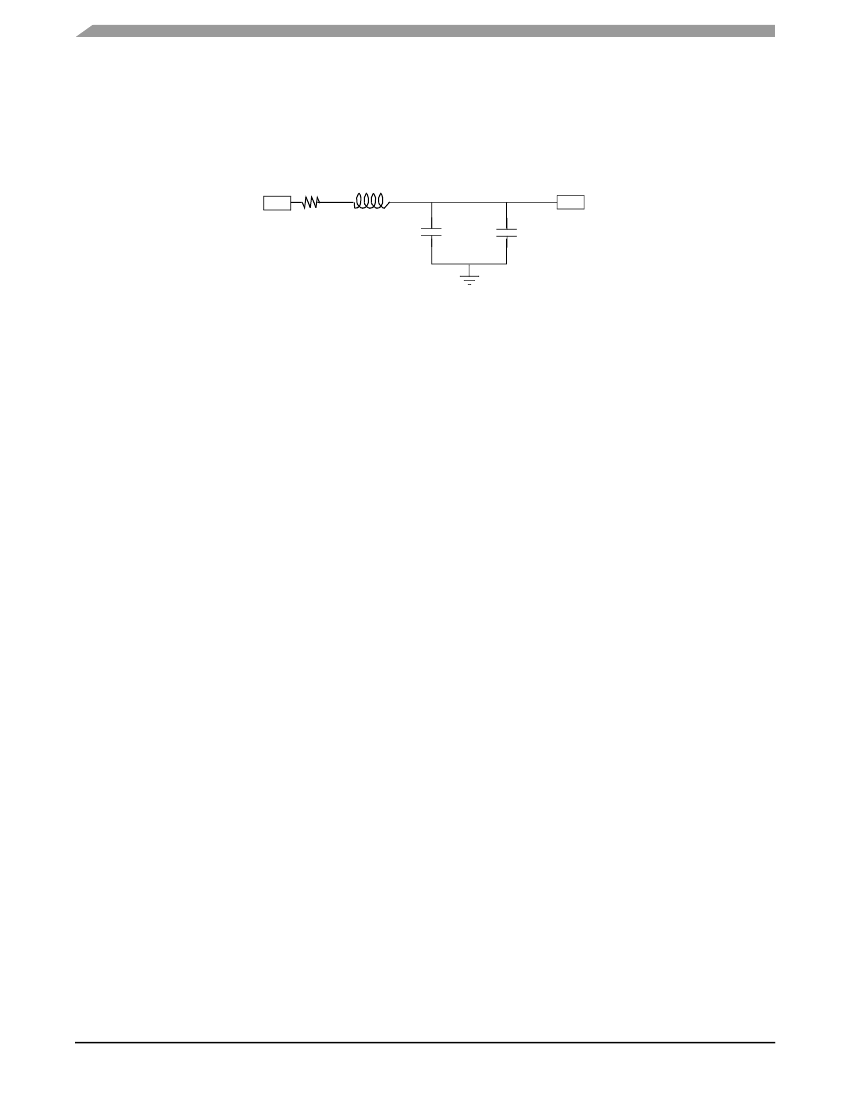

SYN

and

GND

SYN1

should be provided with an extremely low impedance path to ground and should be bypassed

to

V

CCSYN

and

V

CCSYN1

, respectively, by a 0.01-碌F capacitor located as close as possible to the chip package. The

user should also bypass

GND

SYN

and

GND

SYN1

to

V

CCSYN

and

V

CCSYN1

with a 0.01-碌F capacitor as closely as

possible to the chip package

V

DD

10鈩?/div>

10nH

10 碌F

0.01 碌F

V

CCSYN

Figure 0-1.

VCCSYN and VCCSYN1 Bypass

MSC8101 Technical Data, Rev. 16

4-4

Freescale Semiconductor